# INTEGRATED CIRCUITS

# DATA SHEET

# **TELX family**Low voltage 8-bit microcontrollers

Preliminary specification

File under Integrated Circuits, IC20

1997 Jul 02

# **TELX** family

# **CONTENTS**

| 1    | FEATURES                                        |

|------|-------------------------------------------------|

| 2    | GENERAL DESCRIPTION                             |

| 3    | BLOCK DIAGRAM                                   |

| 4    | FUNCTIONAL DESCRIPTION                          |

| 4.1  | General                                         |

| 4.2  | CPU timing                                      |

| 4.3  | Clocking concept with prescaler PSC             |

| 4.4  | 32 kHz Real-Time Clock                          |

| 4.5  | Memory organization                             |

| 4.6  | Addressing                                      |

| 4.7  | I/O facilities                                  |

| 4.8  | Timer/event counters                            |

| 4.9  | EEPROM                                          |

| 4.10 | DTMF generator section                          |

| 4.11 | MSK modem                                       |

| 4.12 | I <sup>2</sup> C-bus serial I/O                 |

| 4.13 | Standard serial interface SIO0: UART            |

| 4.14 | Interrupt system                                |

| 4.15 | Idle and Power-down operation                   |

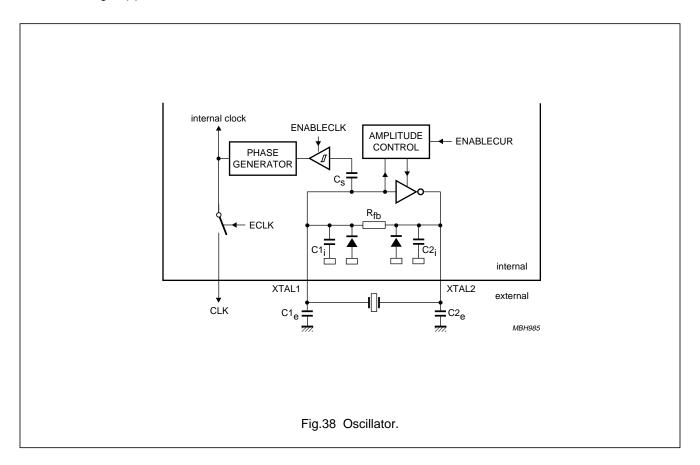

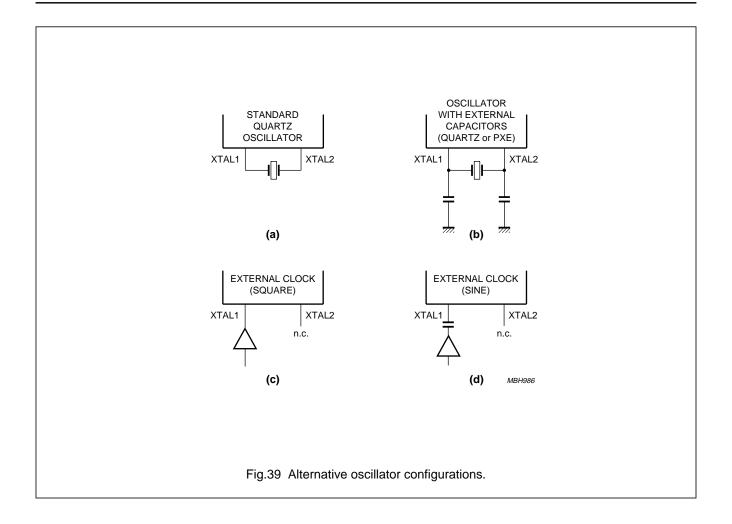

| 4.16 | Oscillator circuitry                            |

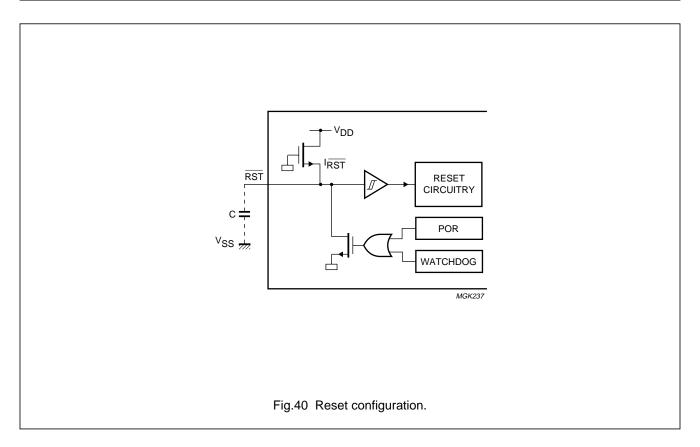

| 4.17 | Reset                                           |

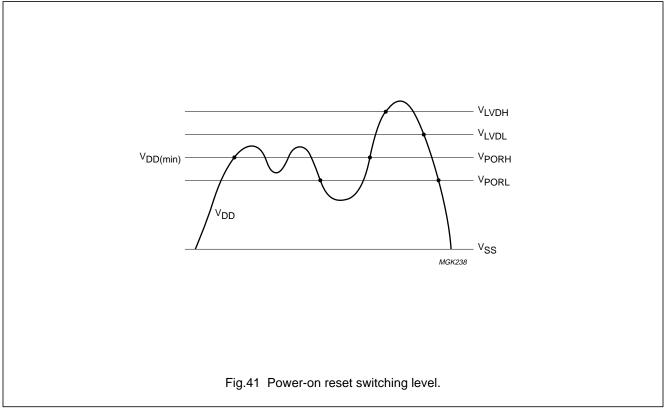

| 4.18 | Low Voltage Detection                           |

| 5    | INSTRUCTION SET                                 |

| 5.1  | Instruction Map                                 |

| 6    | DEFINITIONS                                     |

| 7    | LIFE SUPPORT APPLICATIONS                       |

| 8    | PURCHASE OF PHILIPS I <sup>2</sup> C COMPONENTS |

Philips Semiconductors Preliminary specification

# Low voltage 8-bit microcontrollers

# **TELX** family

#### 1 FEATURES

- Full static 80C51 CPU (8-bit CPU) with a minimum 6 clocks per instruction

- OTP/ROM program memory

- RAM, expandable externally to 64 kbytes (only on certain devices)

- DTMF generator

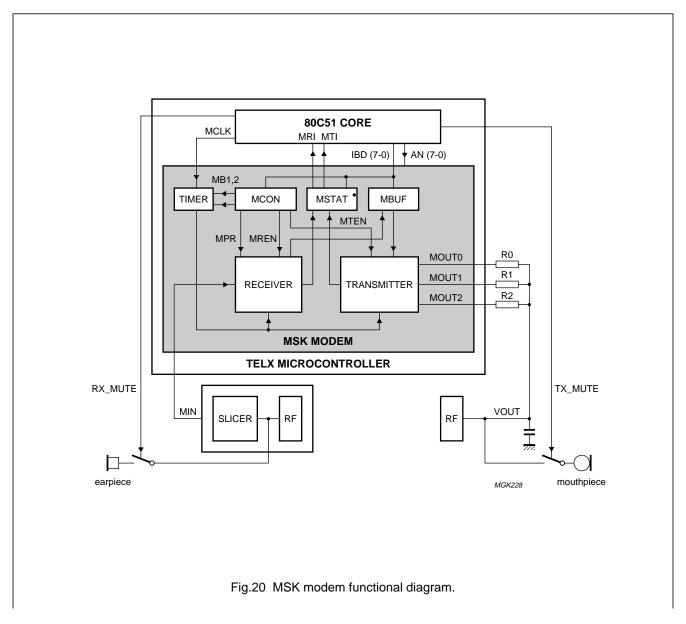

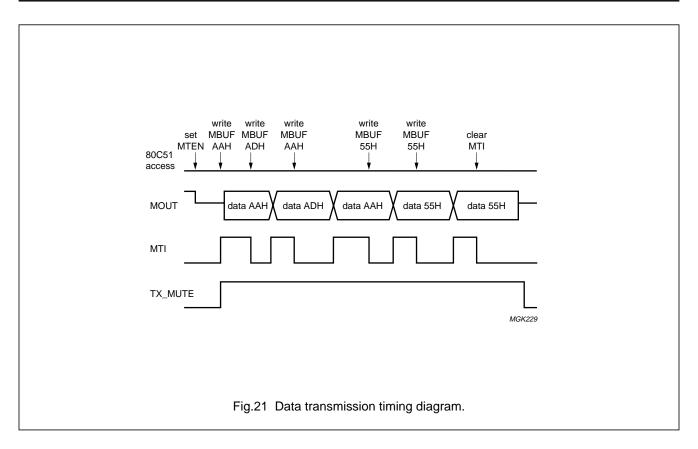

- MSK modem including Manchester encoder/decoder for analog cordless telephones (standards CT0/CT1/CT1+)

- Pulse Width Modulated output (8-bit resolution)

- EEPROM data memory, accessed internally via I<sup>2</sup>C-bus interface

- 8-bit ports, I/O lines

- Three 16-bit timer/event counters, including one with capture, compare and PWM function

- Watchdog Timer

- External memory expandable up to 128 kbytes external ROM up to 64 kbytes and/or RAM up to 64 kbytes (only possible on certain devices)

- On-chip amplitude controlled oscillator (ACO) suitable for quartz crystal or ceramic resonator

- 32 kHz Real-Time Clock (RTC) with programmable interrupt periods

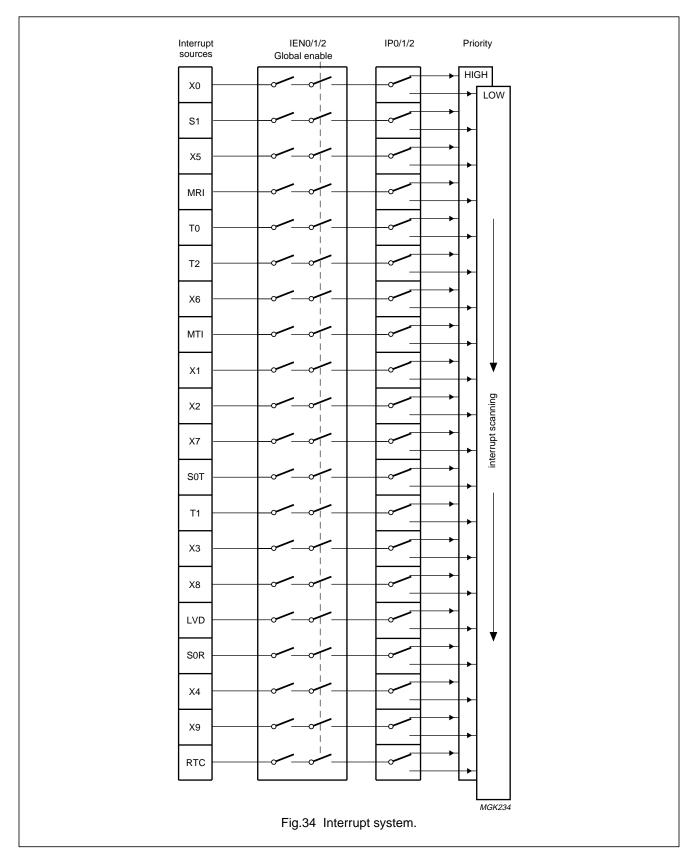

- Twenty source, twenty vector interrupt structure with two priority levels

- Full duplex enhanced UART with double buffering

- I<sup>2</sup>C-bus interface for 2-wire serial transfer, 400 kHz maximum

- Enhanced architecture with:

- Non-page oriented instructions

- Direct addressing

- Four 8 byte RAM register banks

- Stack depth limited only by available internal RAM (maximum 256 bytes)

- Multiply, divide, subtract and compare instructions

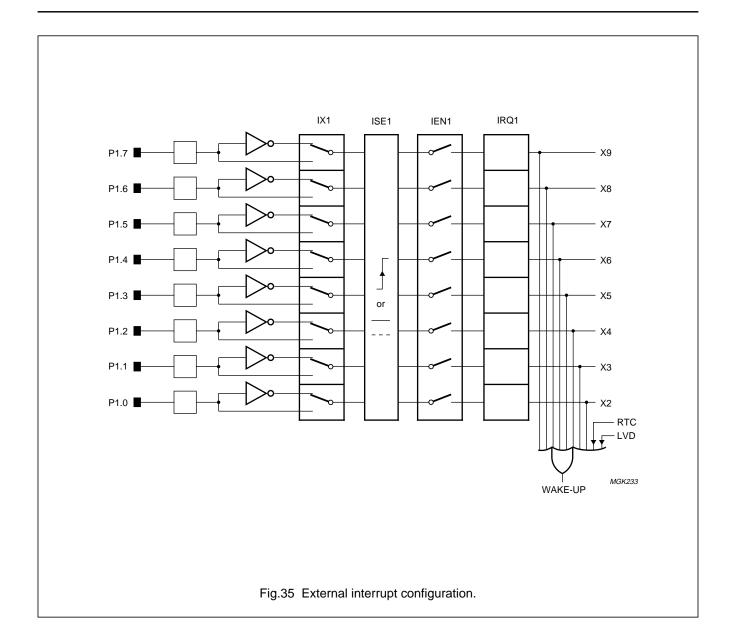

- Eight additional interrupts on Port 1

- Edge or level sensitive triggering selectable via software

- Power-saving use for keyboard control.

- Improved Power-on/Power-off reset circuitry (POR) with 9 hardware programmable levels

- Low Voltage Detection (LVD) with 11 software programmable levels

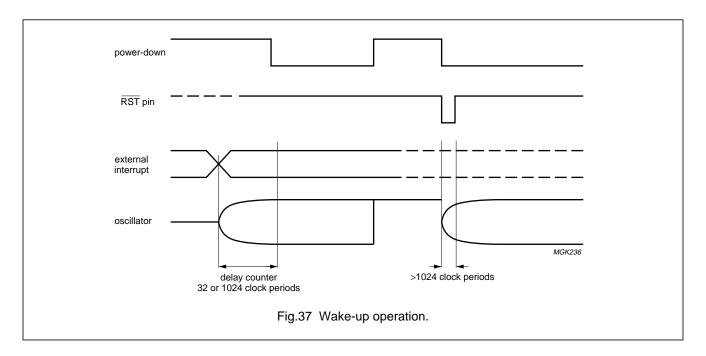

- Wake-up from Power-down mode via external interrupts at Port 1, via RTC or via LVD

- Very low current consumption.

#### 2 GENERAL DESCRIPTION

The TELX microcontroller family is manufactured in an advanced CMOS technology and is based on MCM (Multi-Chip-Module) technology as the non-volatile memory parts OTP and EEPROM are integrated on a separate chip.

The TELX family are 8-bit microcontrollers especially suited for analog cordless telephones (CT0, CT1, CT1+ standards), mid/high-end corded telephones and pagers. For this purpose, features like DTMF, EEPROM, MSK modem, PWM, POR/LVD, ACO and RTC are integrated on-chip. The device is optimized for low power consumption. The TELX family has two software selectable features for power reduction: Idle and Power-down modes.

The instruction set of the TELX family is based on that of the 8051. The TELX family also functions as an arithmetic processor having facilities for both binary and BCD arithmetic plus bit-handling capabilities. The instruction set consists of over 100 instructions: 49 one-byte, 46 two-byte, and 16 three-byte.

This data sheet details the shared properties of the TELX family. For a particular microcontroller, read this data sheet in conjunction with the individual data sheet of the specific device. For details on the I<sup>2</sup>C-bus functions see "Data Handbook IC12".

TELX family

# Low voltage 8-bit microcontrollers

Philips Semiconductors

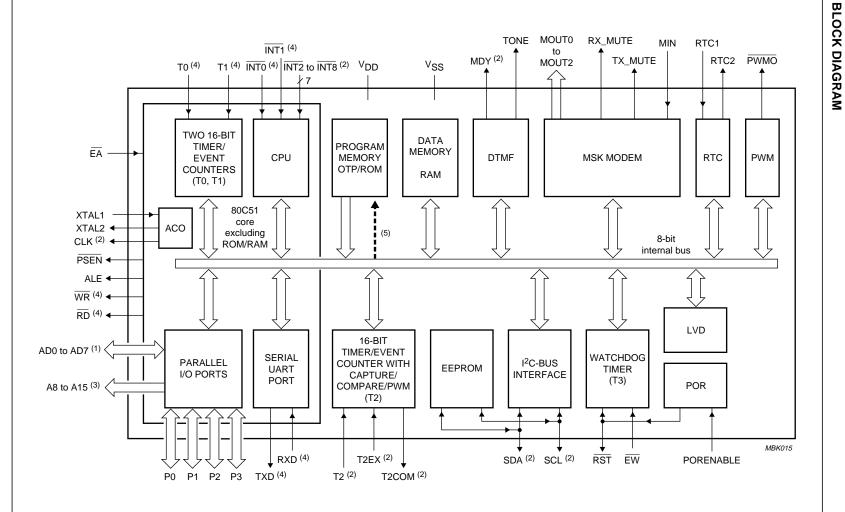

- (1) alternative function of Port 0

- (2) alternative function of Port 1

- (3) alternative function of Port 2

- (4) alternative function of Port 3

- (5) in-circuit OTP programming

Fig.1 Block diagram.

# **TELX** family

#### 4 FUNCTIONAL DESCRIPTION

#### 4.1 General

The TELX family provides stand-alone high-performance CMOS microcontrollers designed for use in mid/high-end corded telephones, analog cordless telephones (CT0, CT1, CT1+ standards) and pagers. For this purpose, features such as DTMF, MSK modem, EEPROM, Real-Time-Clock and PWM have been integrated on-chip. The devices provide hardware features, architectural enhancements and new instructions to function as a controller for applications requiring up to 64 kbytes of program memory and/or up to 64 kbytes of data storage.

The TELX family contains ROM or OTP program memory; a static read/write data memory; I/O lines; three 16-bit timer/event counters; a twenty-source two priority-level, nested interrupt structure and on-chip oscillator and timing circuit.

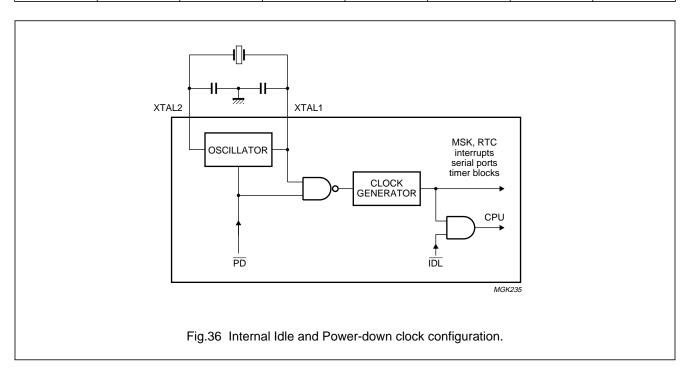

The TELX devices have two software selectable modes of reduced activity for power reduction: Idle and Power-down. The Idle mode freezes the CPU while allowing the RAM, timers, serial I/O and interrupt system to continue functioning. The Power-down mode saves the RAM contents but freezes the oscillator causing all other chip functions to be inoperative.

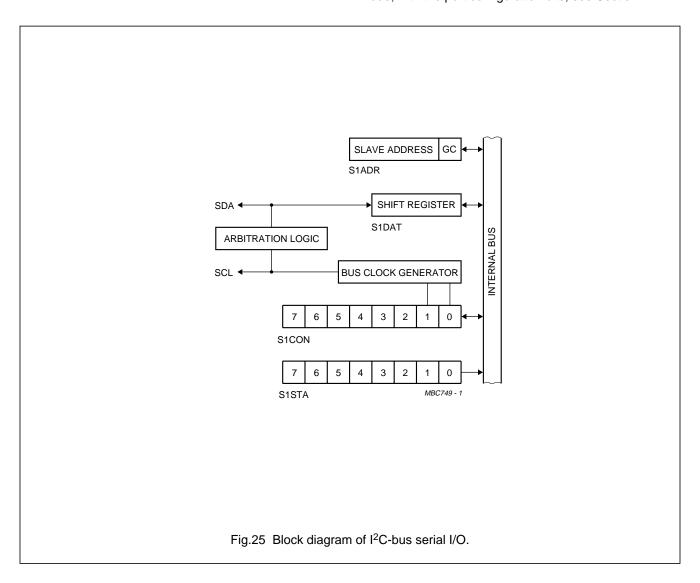

Two serial interfaces are provided on-chip; a standard UART serial interface and an I<sup>2</sup>C-bus serial interface. The I<sup>2</sup>C-bus serial interface has byte orientated master and slave functions allowing communication with the whole family of I<sup>2</sup>C-bus compatible devices.

#### 4.2 CPU timing

A machine cycle consists of a sequence of 6 states. Each state lasts for one oscillator period, thus a machine cycle takes 6 oscillator periods or e.g. 1.68  $\mu$ s if the oscillator frequency is 3.58 MHz. This means that the TELX family is twice as fast as a standard 80C51 based on the same oscillator frequency.

#### 4.3 Clocking concept with prescaler PSC

The clocking concept of the TELX family is shown in Fig.2. The on-chip oscillator directly clocks the CPU (including timers T0 and T1), timer T2, PWM, the Watchdog Timer and the Analog-to-Digital Converter (ADC).

The DTMF block requires an input frequency of 3.58 MHz for correct operation. For this purpose a prescaler (PSC) has been included to enable multiples of 3.58 MHz to be used as the oscillator frequency. The blocks I<sup>2</sup>C-bus, UART special purpose baud rate generator, MSK modem, Watchdog Timer and EEPROM are also clocked via the PSC prescaler to minimize the number of prescalers on-chip and thereby reducing the power consumption. The division factors 1:1 through to 1:8 of the PSC prescaler are software programmable via the PRESC register, see Tables 2 and 3. The PSC division factor should only be set in the initialization routine directly after start-up. The prescaler and the special baud rate timer for the UART are described in Section 4.13.

In order to minimize power consumption, the individual blocks automatically switch-off their clock (gated clock) when they are not enabled.

**TELX** family

# 4.3.1 Prescaler Register (PRESC)

#### Table 1 Prescaler Register (SFR address F3H)

| 7 | 6     | 5     | 4     | 3  | 2   | 1   | 0   |

|---|-------|-------|-------|----|-----|-----|-----|

| _ | PTWO2 | PTWO1 | PTWO0 | P3 | PS2 | PS1 | PS0 |

# Table 2 Description of PRESC bits

| BIT     | SYMBOL | DESCRIPTION                                                                                                     |

|---------|--------|-----------------------------------------------------------------------------------------------------------------|

| PRESC.7 | _      | This bit will always read a logic 0.                                                                            |

| PRESC.6 | PTWO2  | These 3-bits specify the power of two in the division factor of the UART baud rate timer;                       |

| PRESC.5 | PTWO1  | see Section 4.13.3.1.                                                                                           |

| PRESC.4 | PTWO0  |                                                                                                                 |

| PRESC.3 | P3     | This bit specifies the power of three in the division factor of the UART baud rate timer; see Section 4.13.3.1. |

| PRESC.2 | PS2    | These 3-bits select the PSC division factor; see Table 3.                                                       |

| PRESC.1 | PS1    |                                                                                                                 |

| PRESC.0 | PS0    |                                                                                                                 |

Table 3 Selection of PSC division factors

| PS2 | PS1 | PS0 | DIVISION RATIO (f <sub>PSC</sub> : f <sub>osc</sub> ) |

|-----|-----|-----|-------------------------------------------------------|

| 0   | 0   | 0   | 1:1                                                   |

| 0   | 0   | 1   | 1:2                                                   |

| 0   | 1   | 0   | 1:3                                                   |

| 0   | 1   | 1   | 1:4                                                   |

| 1   | 0   | 0   | 1:5                                                   |

| 1   | 0   | 1   | 1:6                                                   |

| 1   | 1   | 0   | 1:7                                                   |

| 1   | 1   | 1   | 1:8                                                   |

# **TELX** family

#### 4.4 32 kHz Real-Time Clock

The Real-Time Clock (RTC) consists of a 32 kHz crystal oscillator, a 32 kHz to 1 second or 1 minute divider chain, an 8-bit Frequency Adjustment Register (FAR) and the Clock Control Register (CLCR). The complete RTC section works independent of the microcontroller status, even in Idle and Power-down mode.

The RTC can generate an interrupt periodically every 1 minute or every 1, 2 or 4 seconds. This interrupt can be used to wake-up the microcontroller from the Power-down mode without resetting it. This feature is especially useful in CTO/CT1 cordless phone applications to wake-up the microcontroller periodically to perform channel scanning.

The internal 32 kHz oscillator requires an external quartz crystal with a frequency of 32.768 kHz (a positive deviation up to +200 ppm is allowed) and an external feedback resistor connected between pins RTC1 and RTC2; 4.7  $M\Omega$  is recommended.

The oscillator is controlled by the RUN bit in the Clock Control Register.

The divider chain operates with the 32 kHz oscillator output and divides this signal down to two clocks with a period of 1, 2 or 4 seconds or 1 minute respectively. Depending on the state of the ITS1 and ITS0 bits in the Clock Control Register, the falling edge of the seconds or minutes clock is used to set the Clock Interrupt Flag (CIF) in the Clock Control Register.

Additionally, the divider chain generates a 16 kHz clock (RTCLK) that can be routed through the port line P1.3/RTCLK, controlled by the ERCO bit in the Clock Control Register.

Frequency adjustment is used to extend the interrupt time by defining the number of 16 kHz clocks in the Frequency Adjustment Register (FAR) that will be counted twice within the first second period after a minute interrupt.

#### 4.4.1 CLOCK CONTROL REGISTER (CLCR)

Table 4 Clock Control Register (address ACH; access type R/W)

| 7    | 6    | 5    | 4   | 3   | 2 | 1    | 0    |

|------|------|------|-----|-----|---|------|------|

| TST2 | TST1 | ERC0 | RUN | CIF | _ | ITS1 | ITS0 |

Table 5 Description of CLCR bits

| BIT | SYMBOL | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|-----|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | TST2   | Test 2 input. This is a testing bit and must be fixed at a logic 0 by user software.                                                                                                                                                                                                                                                                                                                                                                               |

| 6   | TST1   | Test 1 input. This is a testing bit and must be fixed at a logic 0 by user software.                                                                                                                                                                                                                                                                                                                                                                               |

| 5   | ERCO   | Enable 16 kHz Clock Output. If ERCO = 0, then P1.3/RTCLK is a port line. If ERCO = 1, then P1.3/RTCLK is a 16 kHz clock output. ERCO = 1 does not inhibit the port instructions for P1.3/RTCLK. Therefore, the state of both port line and flip-flop may be read in and the port flip-flop may be written by derivative port instructions. However, the port flip-flop of P1.3/RTCLK must remain set to avoid conflicts between the 16 kHz clock and port outputs. |

| 4   | RUN    | Clock Run/Stop. If RUN = 0, then the oscillator is stopped and the clock is reset.  If RUN = 1, then the oscillator and the clock are both running.                                                                                                                                                                                                                                                                                                                |

| 3   | CIF    | Clock Interrupt Flag. Set by hardware, if RTC divider chain overflows (period depending on the state the ITS1 and ITS0 bits) or by software. Reset by software.                                                                                                                                                                                                                                                                                                    |

| 2   |        | Not used.                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 1   | ITS1   | Interrupt Time Select bits. The state of ITS1 and ITS0 determine the interrupt period,                                                                                                                                                                                                                                                                                                                                                                             |

| 0   | ITS0   | see Table 6.                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

**TELX** family

Table 6 Selection of the RTC Interrupt period

| ITS1 | ITS0 | INTERRUPT PERIOD |

|------|------|------------------|

| 0    | 0    | 1 second; note 1 |

| 0    | 1    | 2 seconds        |

| 1    | 0    | 4 seconds        |

| 1    | 1    | 1 minute         |

#### Note

1. If the 1 second interrupt is used, every 60<sup>th</sup> interval may be up to 15.3 ms longer than the others as a result of the frequency adjustment. The adjusted Minute Interrupt Time (MIT) shows now a maximum deviation of 0.5 ppm.

#### 4.4.2 FREQUENCY ADJUSTMENT REGISTER (FAR)

The frequency adjustment value of the RTC section is defined by the 8-bit Frequency Adjustment Register. The register access type is R/W. The significance of the individual bits of the FAR register can be illustrated by the following equation:

Minute interrupt time (MIT) =

$$60 \times 2^{\frac{14}{f_{RTCLK}}} + \frac{FAR}{2^{14}}$$

where  $f_{RTCLK}$  = RTC frequency and FAR represents the decimal value of the contents of the Frequency Adjustment Register.

Table 7

Frequency Adjustment Register (address ADH)

| 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

|------|------|------|------|------|------|------|------|

| FAR7 | FAR6 | FAR5 | FAR4 | FAR3 | FAR2 | FAR1 | FAR0 |

Table 8 Description of FAR bits

| BIT | SYMBOL | DESCRIPTION                                                                          |

|-----|--------|--------------------------------------------------------------------------------------|

| 7   | FAR7   | The state of these 8-bits determine the frequency adjustment value for the Real-Time |

| 6   | FAR6   | Clock; see Table 9.                                                                  |

| 5   | FAR5   |                                                                                      |

| 4   | FAR4   |                                                                                      |

| 3   | FAR3   |                                                                                      |

| 2   | FAR2   |                                                                                      |

| 1   | FAR1   |                                                                                      |

| 0   | FAR0   |                                                                                      |

# **TELX** family

Table 9 Selection of FAR value based on f<sub>RTCLK</sub>

|           | _                  |

|-----------|--------------------|

| FAR (HEX) | f <sub>RTCLK</sub> |

| 00        | 16384.000          |

| 01        | 16384.018          |

| 02        | 16384.033          |

| 03        | 16384.051          |

| 04        | 16384.066          |

| 05        | 16384.084          |

| 06        | 16384.100          |

| 07        | 16384.117          |

| 08        | 16384.135          |

| 09        | 16384.150          |

| 0A        | 16384.168          |

| 0B        | 16384.184          |

| 0C        | 16384.201          |

| 0D        | 16384.217          |

| 0E        | 16384.234          |

| 0F        | 16384.250          |

| 10        | 16384.268          |

| 11        | 16384.283          |

| 12        | 16384.301          |

| 13        | 16384.316          |

| 14        | 16384.334          |

| 15        | 16384.350          |

| 16        | 16384.367          |

| 17        | 16384.385          |

| 18        | 16384.400          |

| 19        | 16384.418          |

| 1A        | 16384.434          |

| 1B        | 16384.451          |

| 1C        | 16384.467          |

| 1D        | 16384.484          |

| 1E        | 16384.500          |

| 1F        | 16384.518          |

| 20        | 16384.533          |

| L         | 1                  |

| FAR (HEX) | f <sub>RTCLK</sub> |

|-----------|--------------------|

| 21        | 16384.551          |

| 22        | 16384.566          |

| 23        | 16384.584          |

| 24        | 16384.600          |

| 25        | 16384.617          |

| 26        | 16384.635          |

| 27        | 16384.650          |

| 28        | 16384.668          |

| 29        | 16384.684          |

| 2A        | 16384.701          |

| 2B        | 16384.717          |

| 2C        | 16384.734          |

| 2D        | 16384.750          |

| 2E        | 16384.768          |

| 2F        | 16384.783          |

| 30        | 16384.801          |

| 31        | 16384.816          |

| 32        | 16384.834          |

| 33        | 16384.850          |

| 34        | 16384.867          |

| 35        | 16384.885          |

| 36        | 16384.900          |

| 37        | 16384.918          |

| 38        | 16384.934          |

| 39        | 16384.951          |

| 3A        | 16384.967          |

| 3B        | 16384.984          |

| 3C        | 16385.000          |

| 3D        | 16385.018          |

| 3E        | 16385.033          |

| 3F        | 16385.051          |

| 40        | 16385.066          |

| 41        | 16385.084          |

# TELX family

| FAR (HEX) | f <sub>RTCLK</sub> |

|-----------|--------------------|

| 42        | 16385.100          |

| 43        | 16385.117          |

| 44        | 16385.135          |

| 45        | 16385.150          |

| 46        | 16385.168          |

| 47        | 16385.184          |

| 48        | 16385.201          |

| 49        | 16385.217          |

| 4A        | 16385.234          |

| 4B        | 16385.250          |

| 4C        | 16385.268          |

| 4D        | 16385.283          |

| 4E        | 16385.301          |

| 4F        | 16385.316          |

| 50        | 16385.334          |

| 51        | 16385.350          |

| 52        | 16385.367          |

| 53        | 16385.385          |

| 54        | 16385.400          |

| 55        | 16385.418          |

| 56        | 16385.434          |

| 57        | 16385.451          |

| 58        | 16385.467          |

| 59        | 16385.484          |

| 5A        | 16385.500          |

| 5B        | 16385.518          |

| 5C        | 16385.533          |

| 5D        | 16385.551          |

| 5E        | 16385.566          |

| 5F        | 16385.584          |

| 60        | 16385.600          |

| 61        | 16385.617          |

| 62        | 16385.635          |

| 63        | 16385.650          |

| FAR (HEX) | f <sub>RTCLK</sub> |

|-----------|--------------------|

| 64        | 16385.668          |

| 65        | 16385.684          |

| 66        | 16385.701          |

| 67        | 16385.717          |

| 68        | 16385.734          |

| 69        | 16385.750          |

| 6A        | 16385.768          |

| 6B        | 16385.783          |

| 6C        | 16385.801          |

| 6D        | 16385.816          |

| 6E        | 16385.834          |

| 6F        | 16385.850          |

| 70        | 16385.867          |

| 71        | 16385.885          |

| 72        | 16385.900          |

| 73        | 16385.918          |

| 74        | 16385.934          |

| 75        | 16385.951          |

| 76        | 16385.967          |

| 77        | 16385.984          |

| 78        | 16386.000          |

| 79        | 16386.018          |

| 7A        | 16386.033          |

| 7B        | 16386.051          |

| 7C        | 16386.066          |

| 7D        | 16386.084          |

| 7E        | 16386.100          |

| 7F        | 16386.117          |

| 80        | 16386.135          |

| 81        | 16386.150          |

| 82        | 16386.168          |

| 83        | 16386.184          |

| 84        | 16386.201          |

| 85        | 16386.217          |

|           |                    |

# TELX family

| FAR (HEX) | f <sub>RTCLK</sub> |

|-----------|--------------------|

| 86        | 16386.234          |

| 87        | 16386.250          |

| 88        | 16386.268          |

| 89        | 16386.283          |

| 8A        | 16386.301          |

| 8B        | 16386.316          |

| 8C        | 16386.334          |

| 8D        | 16386.350          |

| 8E        | 16386.367          |

| 8F        | 16386.385          |

| 90        | 16386.400          |

| 91        | 16386.418          |

| 92        | 16386.434          |

| 93        | 16386.451          |

| 94        | 16386.467          |

| 95        | 16386.484          |

| 96        | 16386.500          |

| 97        | 16386.518          |

| 98        | 16386.533          |

| 99        | 16386.551          |

| 9A        | 16386.566          |

| 9B        | 16386.584          |

| 9C        | 16386.600          |

| 9D        | 16386.617          |

| 9E        | 16386.635          |

| 9F        | 16386.650          |

| A0        | 16386.668          |

| A1        | 16386.684          |

| A2        | 16386.701          |

| A3        | 16386.717          |

| A4        | 16386.734          |

| A5        | 16386.750          |

| A6        | 16386.768          |

| A7        | 16386.783          |

| FAR (HEX) | f <sub>RTCLK</sub> |

|-----------|--------------------|

| A8        | 16386.801          |

| A9        | 16386.816          |

| AA        | 16386.834          |

| AB        | 16386.850          |

| AC        | 16386.867          |

| AD        | 16386.885          |

| AE        | 16386.900          |

| AF        | 16386.918          |

| В0        | 16386.934          |

| B1        | 16386.951          |

| B2        | 16386.967          |

| В3        | 16386.984          |

| B4        | 16387.000          |

| B5        | 16387.018          |

| B6        | 16387.033          |

| В7        | 16387.051          |

| B8        | 16387.066          |

| B9        | 16387.084          |

| BA        | 16387.100          |

| BB        | 16387.117          |

| BC        | 16387.135          |

| BD        | 16387.150          |

| BE        | 16387.168          |

| BF        | 16387.184          |

| C0        | 16387.201          |

| C1        | 16387.217          |

| C2        | 16387.234          |

| C3        | 16387.250          |

| C4        | 16387.268          |

| C5        | 16387.283          |

| C6        | 16387.301          |

| C7        | 16387.316          |

| C8        | 16387.334          |

| C9        | 16387.350          |

# TELX family

| FAR (HEX) | f <sub>RTCLK</sub> |

|-----------|--------------------|

| CA        | 16387.367          |

| СВ        | 16387.385          |

| CC        | 16387.400          |

| CD        | 16387.418          |

| CE        | 16387.434          |

| CF        | 16387.451          |

| D0        | 16387.467          |

| D1        | 16387.484          |

| D2        | 16387.500          |

| D3        | 16387.518          |

| D4        | 16387.533          |

| D5        | 16387.551          |

| D6        | 16387.566          |

| D7        | 16387.584          |

| D8        | 16387.600          |

| D9        | 16387.617          |

| DA        | 16387.635          |

| DB        | 16387.650          |

| DC        | 16387.668          |

| DD        | 16387.684          |

| DE        | 16387.701          |

| DF        | 16387.717          |

| E0        | 16387.734          |

| E1        | 16387.750          |

| E2        | 16387.768          |

| E3        | 16387.783          |

| E4        | 16387.801          |

|           |                    |

| FAR (HEX) | f <sub>RTCLK</sub> |  |  |

|-----------|--------------------|--|--|

| E5        | 16387.816          |  |  |

| E6        | 16387.834          |  |  |

| E7        | 16387.850          |  |  |

| E8        | 16387.867          |  |  |

| E9        | 16387.885          |  |  |

| EA        | 16387.900          |  |  |

| EB        | 16387.918          |  |  |

| EC        | 16387.934          |  |  |

| ED        | 16387.951          |  |  |

| EE        | 16387.967          |  |  |

| EF        | 16387.984          |  |  |

| F0        | 16388.002          |  |  |

| F1        | 16388.018          |  |  |

| F2        | 16388.035          |  |  |

| F3        | 16388.051          |  |  |

| F4        | 16388.068          |  |  |

| F5        | 16388.084          |  |  |

| F6        | 16388.102          |  |  |

| F7        | 16388.117          |  |  |

| F8        | 16388.135          |  |  |

| F9        | 16388.152          |  |  |

| FA        | 16388.168          |  |  |

| FB        | 16388.186          |  |  |

| FC        | 16388.201          |  |  |

| FD        | 16388.219          |  |  |

| FE        | 16388.234          |  |  |

| FF        | 16384.000          |  |  |

# **TELX** family

#### 4.5 Memory organization

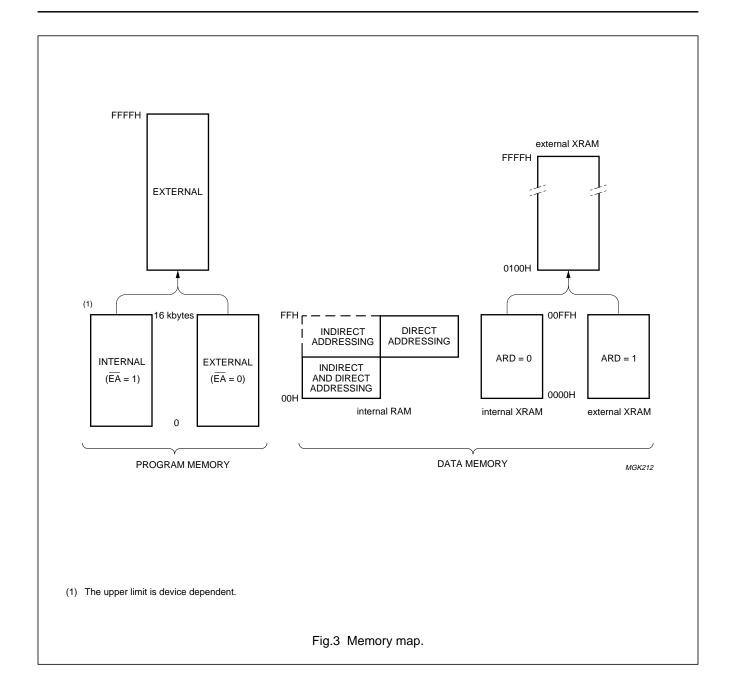

The TELX family has Program Memory (OTP or ROM) plus Data Memory (RAM) on-chip. The device has separate address spaces for Program and Data Memory as shown in Fig.3. On devices with ports P0 and P2 available, up to 64 kbytes of external memory can be addressed. In this case, the CPU generates both read (RD) and write (WR) signals for external Data Memory accesses, and the read strobe (PSEN) for external Program Memory.

#### 4.5.1 Program memory

After reset the CPU begins execution at location 0000H of the Program Memory. The Program Memory can be implemented in either internal OTP/ROM or external memory. If the  $\overline{EA}$  pin is tied to  $V_{DD}$ , then program memory fetches are directed to the internal program memory. If the  $\overline{EA}$  pin is tied to  $V_{SS}$  and if the security bits are not set, then program memory fetches are directed to external memory.

#### 4.5.2 Data memory

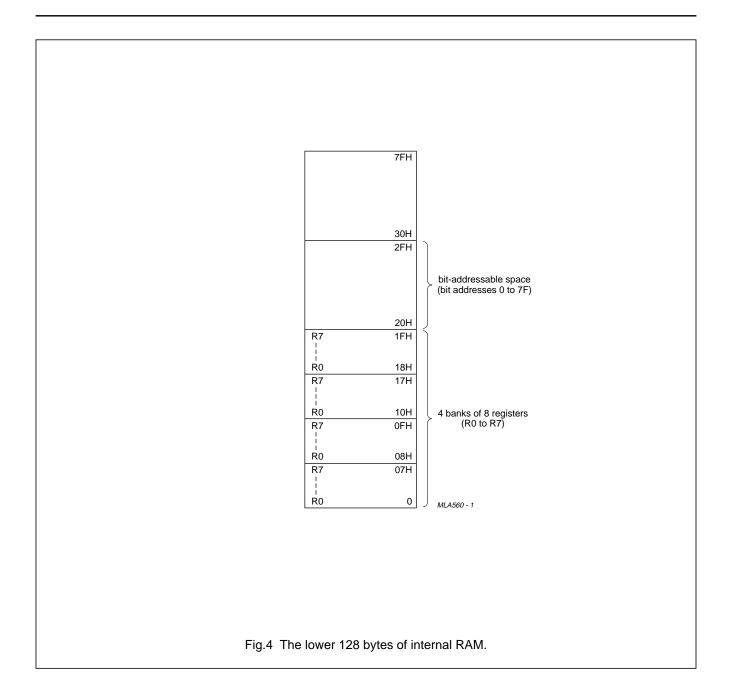

The data memory organisation of the TELX family is exactly the same as for the P8xCE558. The TELX family contains a maximum of 512 bytes internal RAM (consisting of 256 bytes standard RAM and 256 bytes AUX-RAM) and Special Function Registers (SFRs). Figure 3 shows the internal Data Memory space divided into the lower 128 bytes, the upper 128 bytes, the SFR space and 256 bytes Auxiliary RAM. Internal RAM locations 0 to 127 are directly and indirectly addressable. Internal RAM locations 128 to 255 are only indirectly addressable. The SFRs locations 128 to 255 bytes are only directly addressable and the Auxiliary RAM is indirectly addressable as external RAM (MOVX) unless it is disabled by setting ARD = 1.

#### 4.5.3 Special Function Registers

The second 128 bytes are the address locations of the SFRs. Figure 4 and Table 10 define the SFRs memory space. The SFRs include the port latches, timers, peripheral control, serial I/O registers, etc. These registers can only be accessed by direct addressing. There are 128 addressable locations in the SFR address space (those SFRs whose addresses are divisible by eight). Refer to the product specifications for the precise list of the SFRs implemented and their value directly after reset.

#### 4.6 Addressing

The TELX family has five methods for addressing source operands:

- Register

- Direct

- Register-Indirect

- Immediate

- Base-Register plus Index-Register-Indirect.

The first three methods can be used for addressing destination operands. Most instructions have a 'destination/source' field that specifies the data type, addressing methods and operands involved. For operations other than MOVs, the destination operand is also a source operand.

Access to memory addressing is as follows:

- Registers in one of the four 8-register banks through Register Direct or Register-Indirect

- A maximum of 1024 bytes of internal data RAM through Direct or Register-Indirect

- Bytes 0 to 127 of internal RAM may be addressed directly or indirectly. Bytes 128 to 255 of internal RAM share their address location with the Special Function Registers and so may only be addressed indirectly as data RAM

- Bytes 0 to 256 of AUX-RAM can only be addressed indirectly via MOVX instructions.

- Special Function Registers through Direct

- · External data memory through Register-Indirect

- Program memory look-up tables through Base-Register plus Index-Register-Indirect.

The members of the TELX family are classified as 8-bit devices since their internal ROM, RAM, Special Function Registers, Arithmetic Logic Unit and external data bus are all 8-bits wide. All perform operations on bit, nibble, byte and double-byte data types.

Facilities are available for byte transfer, logic and integer arithmetic operations. Data transfer, logic and conditional branch operations can be performed directly on Boolean variables to provide excellent bit handling.

# **TELX** family

# **TELX** family

TELX family

Table 10 Special Function Register memory map (bit addressing)

| REGISTER | START   | REGISTER BIT |      |      |       |       |      |      | END  |         |

|----------|---------|--------------|------|------|-------|-------|------|------|------|---------|

| MNEMONIC | ADDRESS | 0/8          | 1/9  | 2/A  | 3/B   | 4/C   | 5/D  | 6/E  | 7/F  | ADDRESS |

| IP1      | F8H     | PX2          | PX3  | PX4  | PX5   | PX6   | PX7  | PX8  | PX9  | FFH     |

| В        | F0H     | В0           | B1   | B2   | В3    | B4    | B5   | B6   | В7   | F7H     |

| IEN1     | E8H     | EX2          | EX3  | EX4  | EX5   | EX6   | EX7  | EX8  | EX9  | EFH     |

| ACC      | E0H     | ACC0         | ACC1 | ACC2 | ACC3  | ACC4  | ACC5 | ACC6 | ACC7 | E7H     |

| S1CON    | D8H     | CR0          | CR1  | AA   | SI    | STO   | STA  | ENS1 | CR2  | DFH     |

| PSW      | D0H     | Р            | _    | 0V   | RS0   | RS1   | F0   | AC   | CY   | D7H     |

| T2CON    | C8H     | CP/RL2       | C/T2 | TR2  | EXEN2 | ECOMP | COMP | EXF2 | TF2  | CFH     |

| IRQ1     | C0H     | IQ2          | IQ3  | IQ4  | IQ5   | IQ6   | IQ7  | IQ8  | IQ9  | C7H     |

| IP0      | B8H     | PX0          | PT0  | PX1  | PT1   | PS0   | PS1  | PT2  | _    | BFH     |

| P3       | ВОН     | P30          | P31  | P32  | P33   | P34   | P35  | P36  | P37  | В7Н     |

| IEN0     | A8H     | EX0          | ET0  | EX1  | ET1   | ES0R  | ES1  | ET2  | EA   | AFH     |

| P2       | A0H     | P20          | P21  | P22  | P23   | P24   | P25  | P26  | P27  | A7H     |

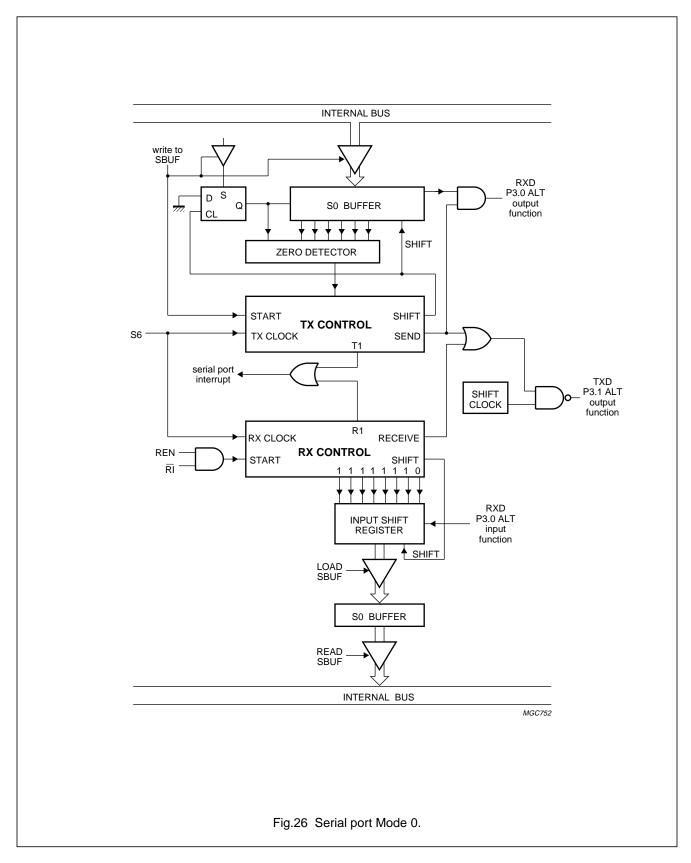

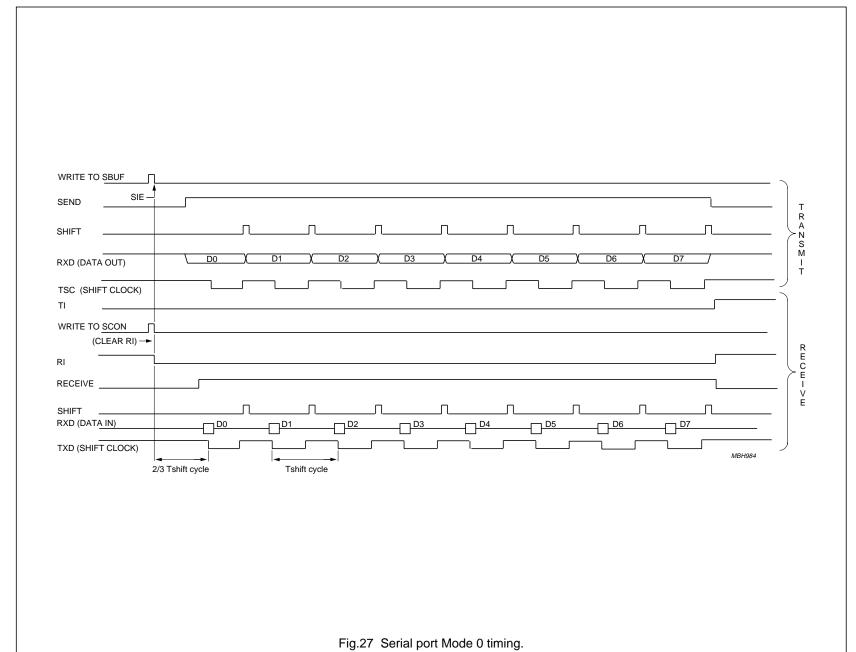

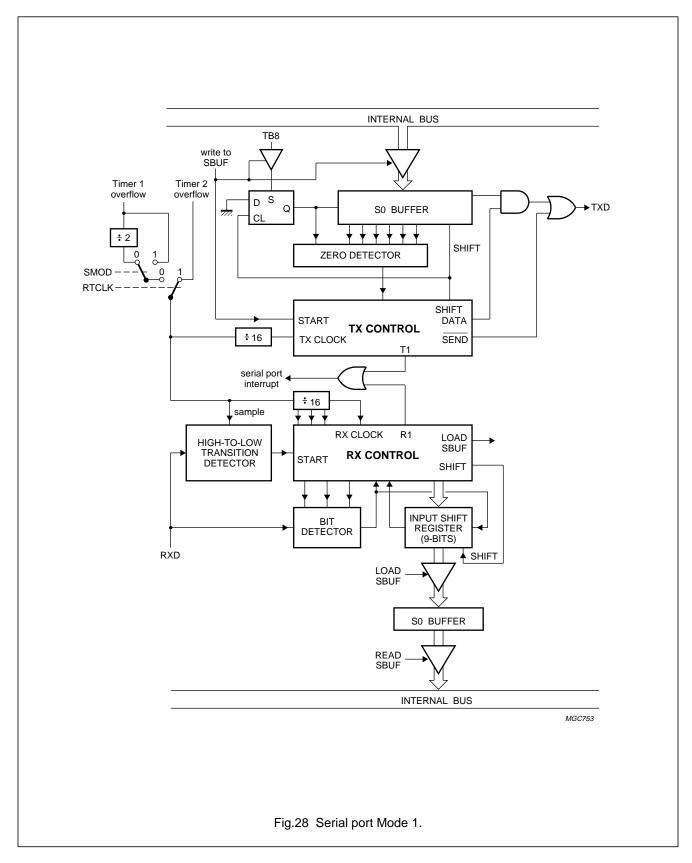

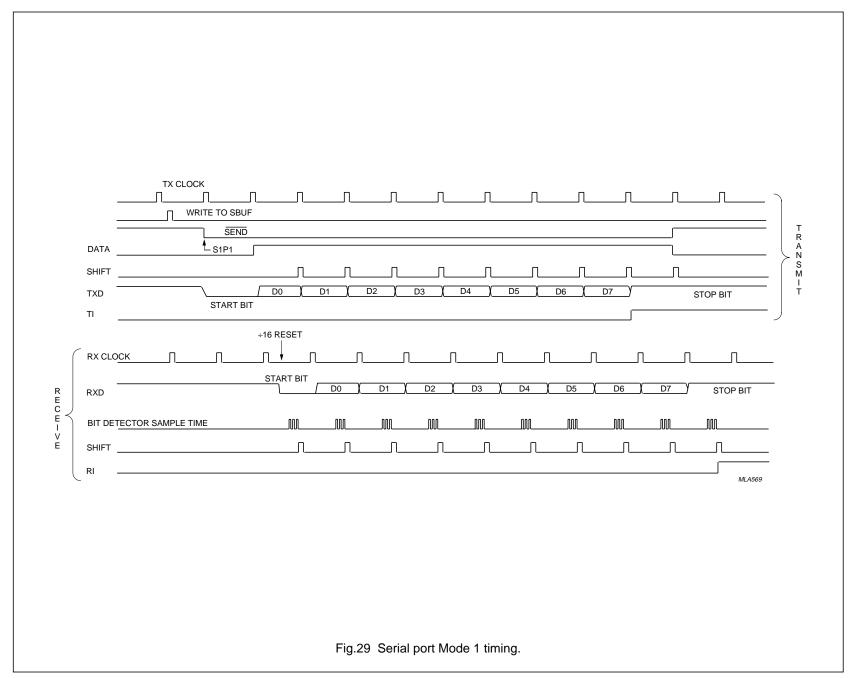

| SOCON    | 98H     | RI           | TI   | RB8  | TB8   | REN   | SM2  | SM1  | SM0  | 9FH     |

| P1       | 90H     | P10          | P11  | P12  | P13   | P14   | P15  | P16  | P17  | 97H     |

| TCON     | 88H     | IT0          | IE0  | IT1  | IE1   | TR0   | TF0  | TR0  | TF1  | 8FH     |

| P0       | 80H     | P00          | P01  | P02  | P03   | P04   | P05  | P06  | P07  | 87H     |

# **TELX** family

#### 4.7 I/O facilities

#### 4.7.1 Ports

The TELX family has 32 I/O lines treated as 32 individually addressable bits or as four parallel 8-bit addressable ports. Ports 0 to 3 perform the following alternative functions.

Port 0 Provides the multiplexed low-order address and data bus for expanding the device with standard memories and peripherals.

Port 1 Used for a number of special functions:

- Provides the inputs for the external interrupts INT2 to INT9

- · External inputs of Timer 2

- External activation and compare output of Timer 2

- Real-Time Clock output (16 kHz)

- · DTMF melody output

- CLK/P1.4 for the clock output

- SCL/P1.6 and SDA/P1.7 for the I<sup>2</sup>C-bus interface are open-drain outputs.

Port 2 Provides the high-order address bus when expanding the device with external program memory and/or external data memory.

Port 3 Pins can be configured individually to provide:

- Serial port receiver input and transmitter output (UART)

- External interrupt request inputs

- · Counter inputs

- Control signals to read and write to external memories.

To enable a port pin alternative function, the port bit latch in its SFR must contain a logic 1.

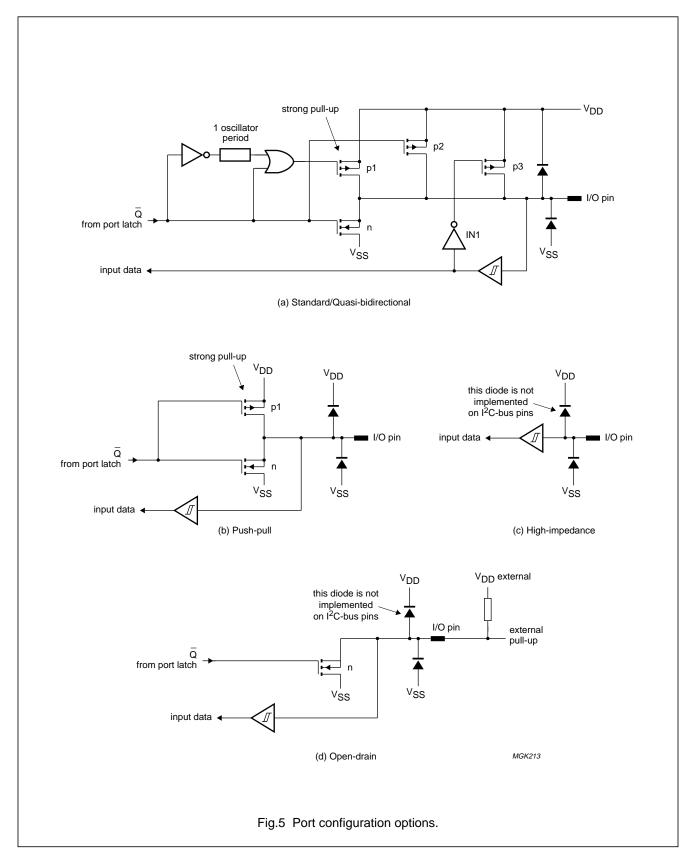

Each port consists of a latch (SFRs P0 to P3), an output driver and input buffer. All ports have internal pull-ups. Figure 5(a) shows that the strong transistor p1 is turned on for only 1 oscillator period after a LOW-to-HIGH transition in the port latch. When on, it turns on p3 (a weak pull-up) through the inverter IN1. This inverter and p3 form a latch which holds the logic 1.

The Alternative Port Function Register (ALTP) is described in Section 4.10.4.

#### 4.7.2 PORT I/O CONFIGURATION

I/O port output configurations are determined by the settings in the port configuration SFRs. Each port has two associated SFRs: PnCFGA and PnCFGB, where 'n' indicates the specific port number (0 to 3). One bit in each of the 2 SFRs relates to the output setting for the corresponding port pin, allowing any combination of the 2 output types to be mixed on those port pins. For example, the output type of Port 1 pin 3 is controlled by setting bit 3 in the SFRs P1CFGA and P1CFGB.

The port pins may be individually configured with one of the following modes (P1.6 and P1.7 can be open-drain or high-impedance but never have any diodes against V<sub>DD</sub>).

- Mode 0 Open-drain; quasi-bidirectional I/O with n-channel open-drain output. Use as an output (e.g. Port 0 for external memory accesses ( $\overline{EA}$  = 0) or access above the built-in memory boundary) requires the connection of an external pull-up resistor. The ESD protection diodes against V<sub>DD</sub> and V<sub>SS</sub> are still present. Except for the I<sup>2</sup>C-bus port (P1.6 and P1.7), ports which are configured as open-drain still have a protection diode to V<sub>DD</sub>. See Fig.5(a).

- Mode 1 Standard Port; quasi-bidirectional I/O with pull-up. The strong pull-up p1 is turned on for only two oscillator periods after a LOW-to-HIGH transition in the port latch. After these two oscillator periods the port is only weakly driven through p2 and 'very weakly' driven through p3. See Fig.5(b).

- Mode 2 High-impedance; this mode turns all port output drivers off. Thus, the pin will not source or sink current and may be used as an input-only pin with no internal drivers for an external device to overcome. See Fig.5(c).

- Mode 3 Push-pull; output with drive capability in both polarities. In this mode, pins can only be used as outputs. See Fig.5(d).

Tables 11 and 12 show the configuration register settings for the four output configurations.

The electrical characteristics of each output type may be found in the DC characteristics in the specific product data sheet.

The default port configuration after reset is also given in the specific product data sheet.

**TELX** family

Table 11 Selection of the port output configuration

| MODE  | PnCFGA  | PnCFGB  | PORT OUTPL                                              | JT CONFIGURATION                           |

|-------|---------|---------|---------------------------------------------------------|--------------------------------------------|

| WIODE | PIICEGA | FIICEGE | NORMAL PORTS                                            | I <sup>2</sup> C-BUS PORTS (P1.6 AND P1.7) |

| 0     | 0       | 0       | 0 open-drain open-drain (port data and I <sup>2</sup> C |                                            |

| 1     | 1       | 0       | quasi-bidirectional                                     | open-drain (port data only)                |

| 2     | 0       | 1       | high-impedance                                          | high-impedance                             |

| 3     | 1       | 1       | push-pull                                               | open-drain (port data only)                |

#### Note

1. If P1CFGA.7 is set the I<sup>2</sup>C-bus interfaces of the microcontroller and other on-chip blocks with an I<sup>2</sup>C-bus interface (e.g. EEPROM) are connected internally. This means that the microcontroller can access these blocks via the I<sup>2</sup>C-bus without using P1.6 and P1.7.

Table 12 Special Function Registers for port configurations; note 1

| REGISTER NAME                    | REGISTER<br>MNEMONIC | SFR ADDRESS<br>(HEX) | STATE AFTER RESET                      |

|----------------------------------|----------------------|----------------------|----------------------------------------|

| Port P0 Configuration A Register | P0CFGA               | 8E                   | depending on product, refer to product |

| Port P0 Configuration B Register | P0CFGB               | 8F                   | specification                          |

| Port P0 output data Register     | P0                   | 80                   |                                        |

| Port P1 Configuration A Register | P1CFGA               | 9E                   |                                        |

| Port P1 Configuration B Register | P1CFGB               | 9F                   |                                        |

| Port P1 output data Register     | P1                   | 90                   |                                        |

| Port P2 Configuration A Register | P2CFGA               | AE                   |                                        |

| Port P2 Configuration B Register | P2CFGB               | AF                   |                                        |

| Port P2 output data Register     | P2                   | A0                   |                                        |

| Port P3 Configuration A Register | P3CFGA               | BE                   |                                        |

| Port P3 Configuration B Register | P3CFGB               | BF                   |                                        |

| Port P3 output data Register     | P3                   | B0                   |                                        |

#### Note

1. Mode changes may cause glitches to occur during transitions. When modifying both registers, WRITE instructions should be carried out consecutively.

# **TELX** family

Philips Semiconductors Preliminary specification

# Low voltage 8-bit microcontrollers

# **TELX** family

#### 4.8 Timer/event counters

The TELX family contains three 16-bit timer/event counters: Timer 0, Timer 1 and Timer 2 which perform the following functions:

- Measure time intervals and pulse durations

- · Count events

- · Generate interrupt requests

- · Generate output on comparator match

- Generate a pulse width modulated output signal.

Timer 0 and Timer 1 can be programmed independently to operate in four modes:

- Mode 0 8-bit timer or 8-bit counter each with divide-by-32 prescaler

- Mode 1 16-bit time-interval or event counter

- Mode 2 8-bit time-interval or event counter with automatic reload upon overflow

- Mode 3 Timer 0 establishes TL0 and TH0 as two separate counters.

In the timer mode the register is incremented every machine cycle. Since a machine cycle consists of a minimum of 6 oscillator periods, the maximum count rate is  $^1\!\!/_6\times f_{\text{osc}}.$

In the counter mode, the register is incremented in response to a HIGH-to-LOW transition. Since it takes one machine cycle (minimum 6 oscillator periods) to recognize a HIGH-to-LOW transition, the maximum count rate is  $1\!\!/_{\!6}\times f_{\text{osc}}.$  To ensure a given level is sampled, it should be held for at least one complete machine cycle.

#### 4.8.1 TIMER T2

Note that the function of Timer 2 may deviate from the following description for certain products in the TELX family. In such a case, the deviation is described in the specific product data sheet.

Timer 2 is a 16-bit timer/counter that can operate as a timer, as an event counter or as a pulse width modulator.

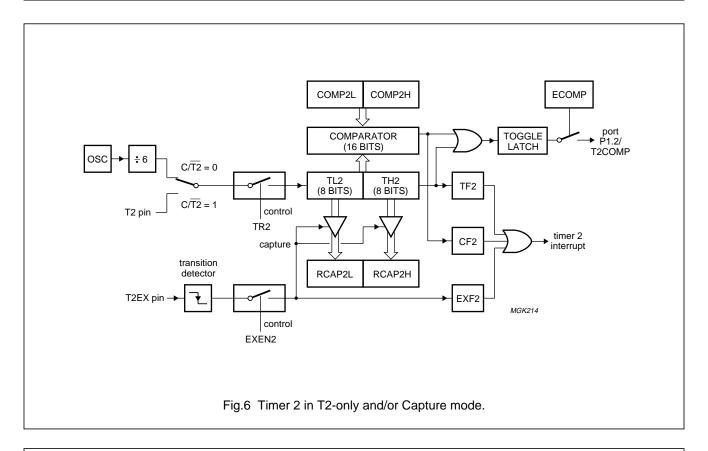

The following operating modes are available: External interrupt, T2-only, Auto-Reload and Capture mode. If Timer 2 is in the OFF state, its clock is switched off and the timer has an extremely low power consumption. Parallel to these operating modes, a Compare function and/or a pulse generator function is provided.

The operating modes are selected via the T2CON bits TR2, CP/RL2 and EXEN2 (see Table 13).

**Table 13** Selection of Timer 2 operating modes

| TR2 | EXEN2 | CP/RL2             | MODE        |

|-----|-------|--------------------|-------------|

| 0   | 0     | Х                  | OFF         |

| 0   | 1     | X External interru |             |

| 1   | Х     | 0                  | Auto-reload |

| 1   | 0     | 1                  | T2-only     |

| 1   | 1     | 1                  | Capture     |

In the T2-only mode, TH2 and TL2 function as a 16-bit timer or counter which upon overflowing sets the Timer 2 overflow bit TF2. This may then be used to generate an interrupt.

In the Capture mode, TH2 and TL2 function as a 16-bit timer or counter which upon overflowing sets the Timer 2 overflow bit TF2. This may then be used to generate an interrupt. Additionally a HIGH-to-LOW transition at external input T2EX causes the current value in TL2 and TH2 to be captured into registers RCAP2L and RCAP2H respectively. In addition, the transition at T2EX causes the EXF2 interrupt flag in T2CON to be set, this may also be used to generate an interrupt. The Capture mode and the T2-only mode are shown in Fig.6.

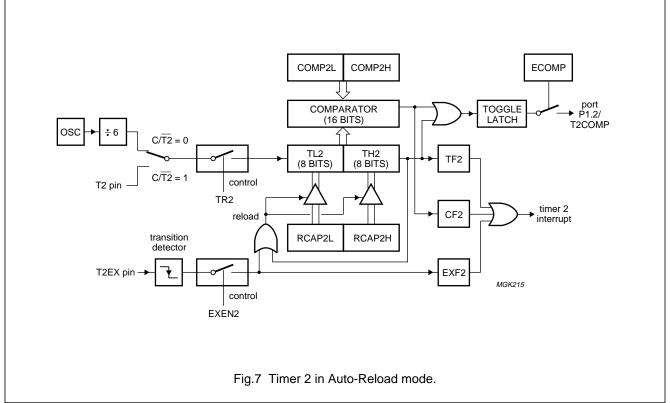

In the Auto-Reload mode the 16-bit counter (TH2, TL2) does not continue counting at the value 0000H, after an overflow occurred, but will be reloaded with the 16-bit value stored in the SFRs RCAP2H and RCAP2L. If in Auto-Reload mode, the EXEN2 bit is set, a HIGH-to-LOW transition at external input T2EX will set the EXF2 bit and will also trigger the reloading of TH2,TL2. The Auto-Reload mode is shown in Fig.7.

# **TELX** family

# **TELX** family

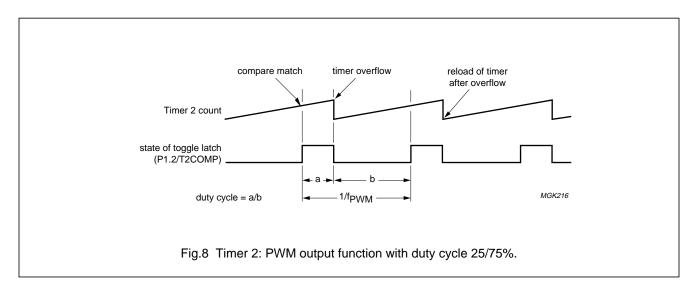

Parallel to the T2-only, Capture and Auto-Reload mode, a compare function can be activated by writing a value other than 0000H to the compare SFRs COMP2H and COMP2L. A compare match is generated when the timer register TL2/TH2 increments to the value of the compare register COMP2L/COM2H. A compare match will set the compare flag CF2, this may also be used to generate an interrupt.

Parallel to the T2-only, Capture and Auto-Reload mode, a Pulse Width Modulation function can be activated by setting the ECOMP bit in the T2CON register. This will activate the alternative port function T2COMP for port bit P1.2. Every time a compare match or a timer overflow occurs, P1.2 (T2COMP) is toggled. The initial state of P1.2 after setting ECOMP is LOW.

If this pulse function is used in conjunction with the Auto-Reload mode and the compare function, a Pulse Width Modulation (PWM) function is realized. The PWM frequency is given by the reload value stored in register RCAP2L/RCAP2H. The PWM duty cycle is given by the value stored in register COMP2L/COMP2H. In Fig.8 an example of this is given with a 25/75% duty cycle.

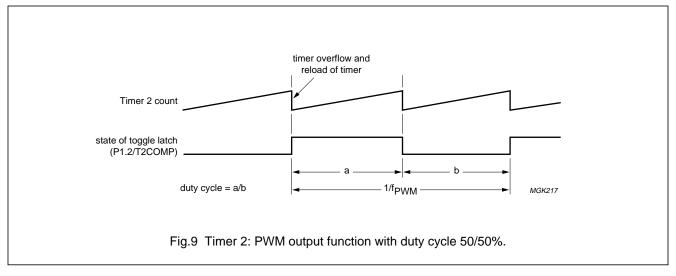

As a special case, if both registers COMP2H and COMP2L are reset, the frequency on pin P1.2/T2COMP will be given only by the value of the reload register RCAP2L/RCAP2H and is half the frequency for an active compare. The duty cycle will be 50% as shown in Fig.9.

**TELX** family

# 4.8.2 TIMER/COUNTER 2 CONTROL REGISTER (T2CON)

Table 14 Timer/Counter 2 Control Register (SFR address C8H)

| 7   | 6    | 5   | 4     | 3     | 2   | 1    | 0      |

|-----|------|-----|-------|-------|-----|------|--------|

| TF2 | EXF2 | CF2 | ECOMP | EXEN2 | TR2 | C/T2 | CP/RL2 |

Table 15 Description of T2CON bits

| BIT     | SYMBOL | DESCRIPTION                                                                                                                                                                                                                                                                                                                                 |

|---------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| T2CON.7 | TF2    | <b>Timer 2 overflow flag.</b> TF2 is set by a Timer 2 overflow and must be cleared by software. When Timer T2 interrupt is enabled, TF2 = 1 will cause the CPU to vector to Timer 2 interrupt routine. TF2 must be cleared by software. TF2 can also be set by software.                                                                    |

| T2CON.6 | EXF2   | <b>Timer 2 external flag.</b> EXF2 is set when either a capture or reload is caused by a negative transition on T2EX and when EXEN2 = 1. When Timer T2 interrupt is enabled, EXF2 = 1 will cause the CPU to vector to Timer 2 interrupt routine. EXF2 must be cleared by software. EXF2 can also be set by software.                        |

| T2CON.5 | CF2    | Compare flag. CF2 is set by hardware if the timer register TL2/TH2 increments to the value of the compare register COMP2L/COMP2H. CF2 must be cleared by software. When Timer T2 interrupt is enabled, CF2 = 1 will cause the CPU to vector to Timer 2 interrupt routine. CF2 must be cleared by software. CF2 can also be set by software. |

| T2CON.4 | ECOMP  | <b>Enable compare.</b> When set by software, the controller toggles port bit P1.2 (T2COMP) every time a compare match or a timer overflow occurs. The toggle latch connected to port P1.2/T2COMP is reset when bit ECOMP is cleared.                                                                                                        |

| T2CON.3 | EXEN2  | <b>Timer 2 external enable flag.</b> When set, allows a capture or reload to occur as a result of a negative transition on T2EX. EXEN2 = 0 causes Timer 2 to ignore events at T2EX.                                                                                                                                                         |

| T2CON.2 | TR2    | <b>Timer 2 start/stop control.</b> If TR2 is set, the 16-bit counter (TH2,TL2) will start counting.                                                                                                                                                                                                                                         |

| T2CON.1 | C/T2   | <b>Timer 2 timer or counter select.</b> $C/\overline{T2} = 0$ selects the internal timer with a clock frequency of $\frac{1}{6} \times f_{osc}$ . $C/\overline{T2} = 1$ selects the external event counter; negative edge-triggered.                                                                                                        |

| T2CON.0 | CP/RL2 | <b>Capture/reload flag.</b> When set captures will occur on negative transitions at T2EX, if EXEN2 = 1. When cleared, auto-reloads will occur either with Timer 2 overflows or negative transitions at T2EX when EXEN2 = 1.                                                                                                                 |

**TELX** family

#### 4.8.3 WATCHDOG TIMER

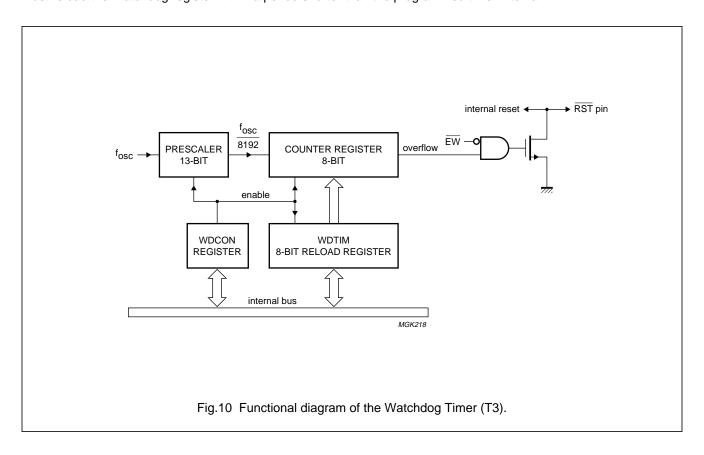

In addition to the standard timers and Timer 2, a Watchdog Timer consisting of an 13-bit prescaler and an 8-bit timer WDTIM is also incorporated. The prescaler is incremented by the external clock. The 8-bit timer is incremented every 8192 clock cycles.

If the clock frequency is 3.58 MHz, the Watchdog Timer can operate in the range of 2.3 ms up to 0.56 s. The Watchdog Timer is disabled after reset. It can be enabled by writing any value to the WDCON register. A running Watchdog Timer will only be disabled if the microcontroller enters Power-down mode or if the microcontroller is reset.

When a timer overflow occurs and the Watchdog Enable pin  $(\overline{\text{EW}})$  is LOW, the reset pin  $(\overline{\text{RST}})$  will be activated (pulled-down) and the microcontroller will be reset. To prevent an overflow of the Watchdog Timer, the user program must reload the Watchdog register within a period shorter than the programmed timer interval.

**TELX** family

#### 4.8.4 WATCHDOG TIMER INTERVAL REGISTER (WDTIM)

The reset value of WDTIM is 00H. The WDTIM register can only be written to if the WDCON register contains the value 5AH. The Watchdog Timer period can be calculated as follows:

Watchdog period =

$$\frac{(256 - WDTIM) \times 8192}{f_{osc}}$$

Table 16 Watchdog Timer Interval Register (SFR address FFH)

| 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|-----|-----|-----|-----|-----|-----|-----|-----|

| WD7 | WD6 | WD5 | WD4 | WD3 | WD2 | WD1 | WD0 |

Table 17 Description of WDTIM bits

| BIT                | SYMBOL     | DESCRIPTION                                                    |

|--------------------|------------|----------------------------------------------------------------|

| WDTIM.7 to WDTIM.0 | WD7 to WD0 | The state of these 8-bits determine the Watchdog Timer period. |

#### 4.8.5 WATCHDOG TIMER CONTROL REGISTER (WDCON)

The Watchdog Timer is controlled by the WDCON register. A value of A5H in WDCON clears both the prescaler and the timer WDTIM. After reset WDCON contains the value A5H. Every value other than A5H in WDCON enables the Watchdog Timer. Since the WD0 bit of the WDCON input is tied to a logic 0 by hardware during write operations to WDCON, the reset value A5H can not be programmed again and can only be restored by a reset.

Timer WDTIM can be written only if WDCON has previously been loaded with 5AH, otherwise WDTIM and the prescaler are not affected. A successful write operation to WDTIM also clears the prescaler and clears WDCON.

Only the values A5H and 5AH are stored, all other values are stored with a dummy value 00H.

Table 18 Watchdog Control Register (SFR address A5H)

| 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|-----|-----|-----|-----|-----|-----|-----|-----|

| WC7 | WC6 | WC5 | WC4 | WC3 | WC2 | WC1 | WC0 |

Table 19 Description of WDCON bits

| BIT SYMBOL         |            | DESCRIPTION                 |

|--------------------|------------|-----------------------------|

| WDCON.7 to WDCON.0 | WC7 to WC0 | Watchdog Timer control bits |

# **TELX** family

#### 4.8.6 PULSE WIDTH MODULATED OUTPUT

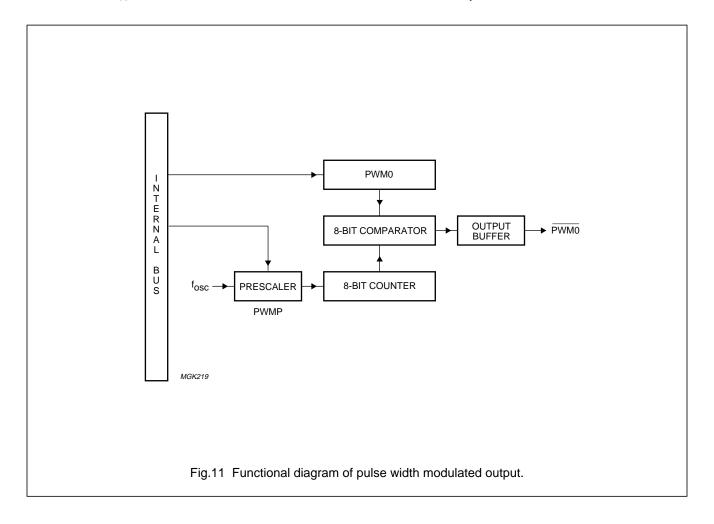

One pulse width modulated output channel is provided which outputs pulses of programmable length and interval. The repetition frequency is defined by an 8-bit prescaler (PWMP) that generates the clock for the counter. The 8-bit counter counts modulo 255 i.e. from 0 to 254 inclusive. The value held in the 8-bit counter is compared to the contents of the register PWM0. Provided the contents of this register are greater than the counter value, the PWM0 output is set LOW. If the contents of register PWM0 are equal to, or less than the counter value, the PWM0 output is set HIGH. The pulse-width-ratio is therefore defined by the contents of register PWM0. The pulse-width-ratio will be in the range 0 to 255/255 and may be programmed in increments of  $\frac{1}{255}$ .

The repetition frequency at the PWM0 output is given by:

$$f_{PWM} = \frac{f_{osc}}{[(1 + PWMP) \times 255]}$$

When using an oscillator frequency of 3.58 MHz for example, the above formula gives a repetition frequency range of 55 Hz to 14 kHz.

By loading the PWMO register with either 00H or FFH, the PWMO output can be maintained at a constant HIGH or LOW level respectively. When loading FFH into the PWMO register, the 8-bit counter will never actually reach this value.

The PWM0 output pin is driven by push-pull drivers and is not shared with any other function.

**TELX** family

#### 4.8.7 Prescaler Frequency Control Register (PWMP)

#### Table 20 Prescaler Frequency Control Register (SFR address FEH)

| 7      | 6      | 5      | 4      | 3      | 2      | 1      | 0      |

|--------|--------|--------|--------|--------|--------|--------|--------|

| PWMP.7 | PWMP.6 | PWMP.5 | PWMP.4 | PWMP.3 | PWMP.2 | PWMP.1 | PWMP.0 |

#### Table 21 Description of PWMP bits

| BIT SYMBOL |                 | DESCRIPTION                            |

|------------|-----------------|----------------------------------------|

| 7 to 0     | PWMP7 to PWMP.0 | prescaler division factor = (PWMP) + 1 |

#### 4.8.8 Pulse Width Modulated Register (PWM0)

# Table 22 Pulse Width Modulated Register (SFR address FCH)

| 7      | 6      | 5      | 4      | 3      | 2      | 1      | 0      |

|--------|--------|--------|--------|--------|--------|--------|--------|

| PWM0.7 | PWM0.6 | PWM0.5 | PWM0.4 | PWM0.3 | PWM0.2 | PWM0.1 | PWM0.0 |

#### Table 23 Description of PWM0 bits

| BIT    | SYMBOL          | DESCRIPTION                                |

|--------|-----------------|--------------------------------------------|

| 7 to 0 | PWM07 to PWM0.0 | These 8-bits define the pulse-width-ratio. |

# **TELX** family

#### 4.9 EEPROM

#### 4.9.1 GENERAL DESCRIPTION

Most microcontrollers in the TELX family contain an on-chip low-power Electrically Erasable Programmable ROM (EEPROM) memory for non-volatile data storage. The memory offers the following features:

- · Low power consumption

- No current consumption if the EEPROM is disabled (see Section 4.9.6)

- Single supply programming; the programming voltage is generated internally via an on-chip voltage multiplier

- Automatic ERASE before WRITE when programming

- User defined programming time (see Section 4.9.6)

- Page programming; 1 to 8 bytes can be programmed simultaneously, reducing programming time

- Accessible via I<sup>2</sup>C-bus:

- Fixed slave address

- Operates in Slave Transmitter or Slave Receiver modes

- Can be accessed from a master connected to the external I<sup>2</sup>C-bus (EEPROM access in external mode)

- Can be accessed from the host master even if ports P1.6 and P1.7 are not used as I<sup>2</sup>C-bus pins (EEPROM access in internal mode)

- Supports continuous read and page-write, (word address automatically incremented).

#### 4.9.2 I<sup>2</sup>C-BUS OPERATION

The operation of the EEPROM memory depends on the state of the I<sup>2</sup>C-bus interface (see Section 4.12) and of the port pins P1.6 and P1.7 (see Section 4.7.2). Three situations are possible:

EEPROM access in internal mode. The I<sup>2</sup>C-bus serial I/O interface and the EEPROM memory are active, but the port pins P1.6 and P1.7 are not used as I<sup>2</sup>C-bus pins.

The CPU of the TELX microcontroller can program and read the EEPROM. Port pins P1.6 and P1.7 can be used as open-drain ports for other purposes.

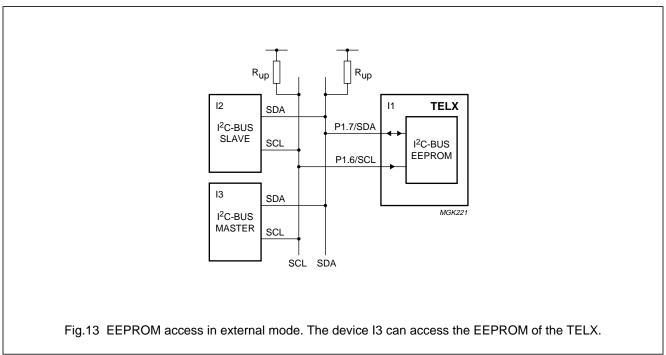

2. **EEPROM** access in external mode. The I<sup>2</sup>C-bus serial I/O master is not active, port pins P1.6 and P1.7 are configured as I<sup>2</sup>C-bus pins, and the EEPROM is active.

The EEPROM can be accessed from a master connected to the I<sup>2</sup>C-bus (see Fig.13), but not from the TELX CPU.

EEPROM access in mixed mode. Both the serial I/O interface and EEPROM are active, P1.6 and P1.7 are configured as I<sup>2</sup>C-bus pins.

Both the CPU of the TELX and external master(s) can read/programme the EEPROM.

After reset, the I<sup>2</sup>C-bus is in internal mode. In external mode, I<sup>2</sup>C-bus pull-up resistors must be connected to P1.6 and P1.7.

Table 24 EEPROM modes of operation

|                                | CONTROL REGISTER |                   |          |                   |                      |          |  |  |

|--------------------------------|------------------|-------------------|----------|-------------------|----------------------|----------|--|--|

| MODE                           | PnCF             | GA <sup>(1)</sup> | PnCF     | GB <sup>(1)</sup> | S1CON <sup>(2)</sup> | EECON(3) |  |  |

|                                | P1CFGA.6         | P1CFGA.7          | P1CFGB.6 | P1CFGB.7          | ENS1                 | EEPE     |  |  |

| EEPROM disabled <sup>(4)</sup> | Х                | Х                 | Х        | Х                 | Х                    | 0        |  |  |

| Internal mode                  | Х                | 1                 | Х        | Х                 | 1                    | 1        |  |  |

| External mode                  | 0                | 0                 | 0        | 0                 | 0                    | 1        |  |  |

| Mixed mode                     | 0                | 0                 | 0        | 0                 | 1                    | 1        |  |  |

#### **Notes**

- 1. See Section 4.7.2, Table 11.

- 2. See Section 4.12.

- 3. See Section 4.9.6.

- 4. When disabled, the EEPROM will not acknowledge any I<sup>2</sup>C-bus request, and consumes no power.

# **TELX** family

# **TELX** family

#### 4.9.3 EEPROM ADDRESSING AND OPERATION

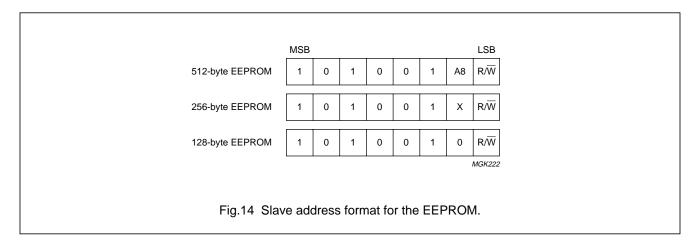

The EEPROM is accessed with an  $I^2C$  Start (S) condition, followed by a 7-bit slave address and a control bit (R/W). Upon successful decoding of the address, the EEPROM answers with an  $I^2C$  Acknowledge (A). Figure 14 shows the slave addresses for the different EEPROM sizes.

In microcontrollers with a 512-byte EEPROM, the 7<sup>th</sup> bit (A8) sent after the 6-bit slave address is part of the word address (A8 is the most significant address bit of the 512-byte EEPROM array).

The last bit of the slave address (R/W) defines the operation to be performed. When set to logic 1 a read operation is selected (the EEPROM will output the addressed data onto SDA at every SCL pulse), and when set to logic 0 the EEPROM will be ready to accept 7 bits of EEPROM address, possibly followed by data bytes to be stored in the EEPROM.

The master can abort any Read or Write operation at any time during I<sup>2</sup>C-bus data transfer by generating a new Start (S) without generating a Stop (P) condition.

#### 4.9.4 WRITE OPERATIONS

#### 4.9.4.1 Byte Write

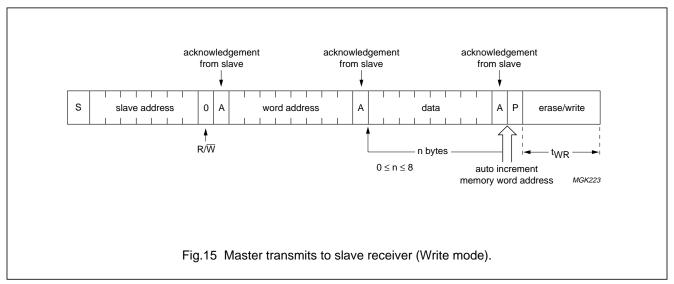

After addressing the EEPROM with the R/W bit set to a logic 0, the EEPROM responds with an acknowledge and expects to receive a word address, followed by a byte of data to be written. In the case of a 512-byte EEPROM, the bit before R/W is the MSB of the word address of the byte to be written (A8). The master then sends the word address (A0 to A7), to which the EEPROM sends an acknowledge (A). Finally the master sends the data to be written, acknowledged by the EEPROM. The master sends a Stop condition (P) to start an Erase/Write cycle. The cycle takes typically 10 ms and is controlled by the E/W control circuitry (see Fig.12). The byte write sequence is shown in Fig.15, for the case n = 1.

Note that a Write to the EEPROM is implemented as a logical OR with the previously stored data; a Write operation must therefore be preceded with an Erase to clear the byte first. The E/W control logic will automatically generate the necessary Erase followed by the Write when a Stop condition is generated. The write time is specified for the complete Erase/Write cycle.

During the Erase/Write cycle the I<sup>2</sup>C-bus interface of the EEPROM is idle, i.e., it does not acknowledge when addressed (see also Section 4.9.4.3).

#### 4.9.4.2 Page Write

In order to reduce total programming time when several bytes of data are to be written to the EEPROM, a page-write operation is available. Up to 8 bytes of data can be programmed with a single Erase/Write cycle, as long as all bytes are on the same page, i.e., their addresses only differ on the 3 lowest bits (A0 to A2). The sequence is similar to the byte-write: the master sends a Start (S) and slave address with the  $R/\overline{W}$  bit set to logic 0, followed by the word address of the first data byte to be programmed.

Then the first data byte is sent, and instead of immediately generating a Stop condition, the master sends up to 7 additional bytes; the 3 lowest bits of the address are automatically incremented, the highest bits remain fixed. The EEPROM acknowledges each data byte. Finally a Stop (P) is generated to start an Erase/Write cycle. This sequence is shown Fig.15.

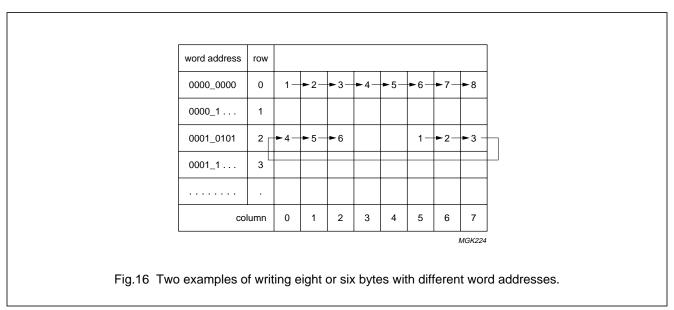

Any number of bytes from 1 to 8 can be written, but their low addresses (A0 to A2) must be sequential. When the page addresses reaches end-of-page (A0 to A2 = 111), the address will wrap around to '000' (binary). Fig.16 shows two examples of possible page set-up; the first example shows eight bytes written starting from the beginning of the page (address 00H), and the second example shows six bytes written starting in the middle of the page, at address 15H.

If more then 8 bytes are sent by the master, the EEPROM will ignore and will **not** acknowledge the 9<sup>th</sup>, 10<sup>th</sup> etc., bytes. The master can proceed in one of two ways:

- Abort the write procedure, by sending a Start (S) and repeating the complete page-write procedure of Fig.15

- Start and Erase/Write cycle by generating a Stop (P).

The first 8 bytes transmitted will be written into the EEPROM cells.

#### 4.9.4.3 Acknowledge Polling

During programming, the EEPROM does not acknowledge when addressed by an I<sup>2</sup>C-bus master. To find out when the EEPROM is again accessible, the microcontroller must perform ACK polling, i.e. repeatedly send a Start and slave address and check if an acknowledge is generated.

# **TELX** family

# **TELX** family

#### 4.9.5 READ OPERATIONS

An unlimited number of data bytes can be read, the address being automatically incremented after each byte is transmitted. A Read can be done in two ways: by first setting the word address (Random Read), or without setting the word address (Current Address Read). Both ways allow to sequentially read any number of bytes (Sequential Read).

#### 4.9.5.1 Current Address Read

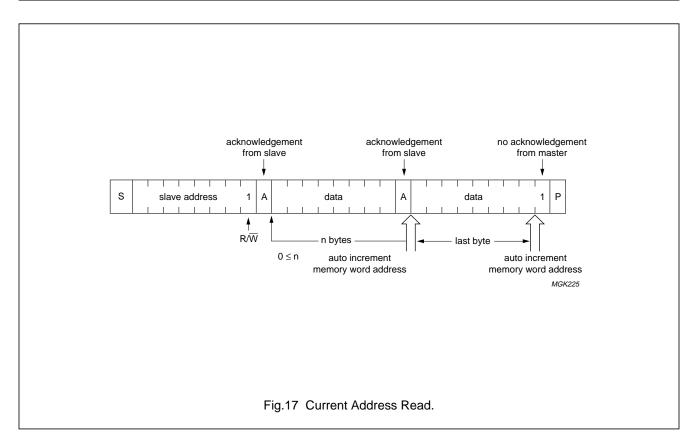

The master addresses the EEPROM slave with the  $R/\overline{W}$  bit set to a logic 1. The EEPROM acknowledges, transmits the data byte addressed by the current contents of the address pointer, and increments it by 1. The master ends the read operation by generating a No-acknowledge (A = 1) and Stop (P).

If the master wishes to read more than one byte (Sequential Read), it generates an Acknowledge (A = 0) after receiving the data byte, and does not generate a Stop. Any number of bytes can be read with this procedure; the address pointer will wrap-around to address 00H when the highest address is read. To end Sequential Read, the master generates a No-acknowledge (A = 1) and a Stop (P). Figure 17 illustrates the Current Address Read and Sequential Read procedure.

When using the Current Address Read, the contents of the address pointer are equal to the address of the byte previously accessed (either by a previous read or write) incremented by 1; e.g., if the previous action was writing or reading byte addressed by 'n', using Current Address Read will retrieve the byte addressed by 'n + 1'.

**Note** there is an exception to the above rule: when using Current Address Read with 512-byte EEPROMs, the MSB of the current read address (A8) is overwritten each time the Slave address is sent. For example, if the byte previously accessed was addressed by 000H, and the EEPROM is selected using A8 = 1, the data retrieved will be in address 101H (A8 = 1, A0 to A7 incremented by 1) and not 001H.

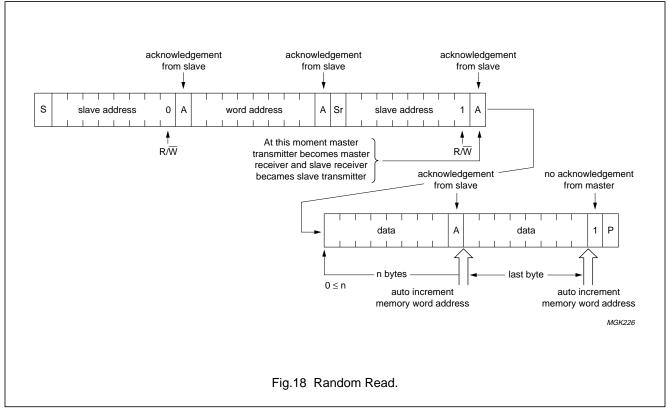

#### 4.9.5.2 Random Read

In Random Read mode, the address of the byte to be read is sent prior to the read. The master selects the EEPROM with the  $R/\overline{W}$  bit set to logic 0 (write), and upon Acknowledge from the EEPROM sends the 8-bit word address, which is loaded into the Address pointer and acknowledged by the EEPROM. The master then sends a Repetitive Start (Sr, a Start without previously having generated a Stop) selecting again the slave with the  $R/\overline{W}$  bit to logic 1 (read). The EEPROM transmits the byte addressed by the address pointer and increments it at the end. The master ends Random Read by generating a No-acknowledge (A = 1) and a Stop (S).

If the master wishes to read more bytes, it generates an Acknowledge (A = 0) after receiving each byte (Sequential Read). Any number of bytes can be read; the address pointer will wrap-around to address 00H when the highest address is read. To end Sequential Read, the master generates a No-acknowledge (A = 1) and a Stop (P). Figure 18 shows the Random Read and Sequential Read procedure.

**Note** when using Random Read with EEPROM memories with 512-bytes, the MSB of the word address (A8) sent during the Write frame is overwritten when the slave is addressed a second time, after the Repetitive Start (Sr). For example, if the word-address sent is 000H (A8 = 0), and the slave address after the Repetitive Start contains A8 = 1, then the data retrieved is addressed by 100H and not 000H.

# **TELX** family

# **TELX** family

#### 4.9.6 EEPROM CONTROL REGISTER (EECON)

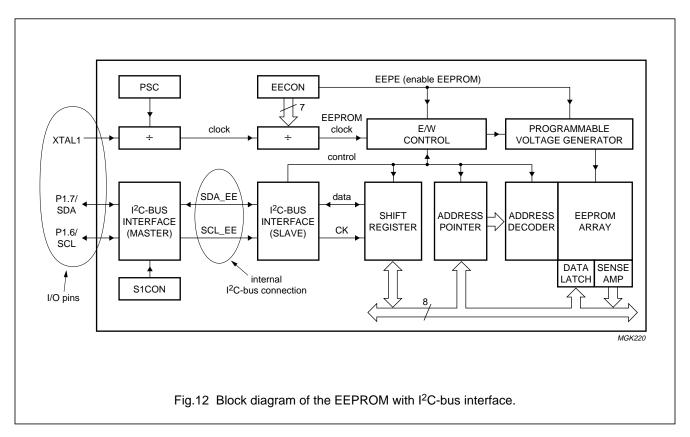

This Special Function Register controls the operation of the EEPROM. The programming time (Erase/Write cycle) is defined by the crystal frequency, the pre-scaler division factor and the EECON bits (EEC0 to EEC6). Erase and Write operations take the same time. Typically 4 to 5 ms are necessary to erase or write the EEPROM cells giving a total Erase/Write cycle time of 8 (minimum) to 10 ms.

To achieve these programming times, the E/W control circuit requires a clock (EEPROM clock, see Fig.12) with a frequency between 51 and 63.75 kHz (max.). Frequencies lower than 51 kHz are acceptable, but result in a programming time greater than 10 ms. The frequency of XTAL is divided by the contents of the PSC register to define the internal clock frequency. This clock is then divided by the contents of the EEC0 to EEC6 bits to generate the 51 kHz EEPROM clock. The Erase and Write times are obtained by further dividing this clock by 255.

The total Erase/Write time is given by the relationship shown below:

$$t_{WR} = 2 \times 255 \times \frac{XTAL1}{PSC \times EECON}$$

To determine the EECON value given the XTAL frequency and the PSC factor the relationship shown below should be used:

$$EECON = \frac{XTAL1 \times t_{WR}}{PSC \times 510}$$

Note that EECON can only take integer values between 2 and 127. Table 27 shows some examples of XTAL frequencies, Prescaler Division Factor and EECON values and the resulting Erase/Write times.

Table 25 EEPROM Control Register (see Section 4.6 for the SFR addressing)

| 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

|------|------|------|------|------|------|------|------|

| EEPE | EEC6 | EEC5 | EEC4 | EEC3 | EEC2 | EEC1 | EEC0 |

Table 26 Description of EECON bits

| BIT    | SYMBOL          | DESCRIPTION                                                                                                                                                                                                                                                                                    |

|--------|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7      | EEPE            | <b>EEPROM Enable.</b> When EEPE = 1, the EEPROM is enabled and can be read and written to. When EEPE = 0, the EEPROM is disabled and in this state consumes no power; reading and writing operations are not possible and the I <sup>2</sup> C-bus interface will not acknowledge any request. |

| 6 to 0 | EEC6 to<br>EEC0 | The decimal value of these 7-bits determines the divider value for the EEPROM programming clock.                                                                                                                                                                                               |

Table 27 EEPROM division factor examples

| XTAL FREQUENCY (MHz) | PSC DIVISION FACTOR | f <sub>PSC</sub><br>(kHz) | EECON VALUE(1) | EEPROM CLOCK<br>FREQUENCY (kHz) | E/W TIME<br>(ms) |

|----------------------|---------------------|---------------------------|----------------|---------------------------------|------------------|

| 30                   | 8                   | 3.75                      | 65 (1100 0001) | 57.7                            | 8.84             |

| 20                   | 6                   | 3.33                      | 57 (1011 1001) | 58.4                            | 8.73             |

| 8.0                  | 2                   | 4.00                      | 69 (1100 0101) | 57.8                            | 8.80             |

| 3.58                 | 1                   | 3.58                      | 62 (1011 1110) | 57.7                            | 8.84             |

| 1.0                  | 1                   | 1.00                      | 17 (1001 0001) | 58.8                            | 8.67             |

| 0.102                | 1                   | 0.102                     | 2 (1000 0010)  | 51.0                            | 10.0             |

#### Note

The EECON division value is in decimal notation and between brackets in binary. The EEPE bit is set to a logic 1 in all cases. The smallest EECON VALUE is 2 (1000 0010). EECON VALUE = 1 (1000 0001) or 0 (1000 0000) generates no EEPROM clock and should not be used.

# **TELX** family

#### 4.10 DTMF generator section

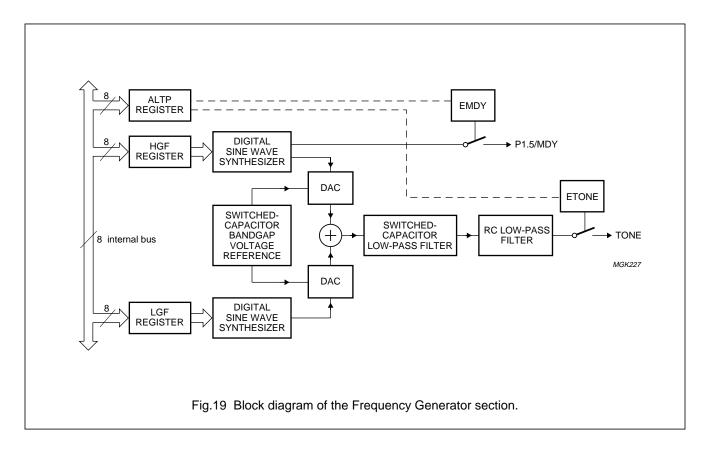

A versatile frequency generator section is provided and is shown in Fig.19. For normal operation use a 3.579545 MHz (or a multiple of this frequency) quartz crystal or PXE resonator. The frequency generator includes precision circuitry for dual-tone multi-frequency (DTMF) signals, which is typically used for tone dialling telephone sets. The TONE output can alternatively issue twelve modem frequencies for data rates between 300 and 1200 bits/s. In addition to DTMF and modem frequencies, two octaves of musical scale in steps of semitones are available.

#### 4.10.1 FREQUENCY REGISTERS

The two frequency registers (LGF and HGF) define two frequencies and from these, the digital sine wave synthesizers together with the Digital-to-Analog Convertors construct two sine waves. Their amplitudes are precisely scaled according to the bandgap voltage reference. This ensures tone output levels independent of supply voltage and temperature.

The amplitude of the Low Group Frequency sine wave is attenuated by 2 dB compared to the amplitude of the High Group Frequency sine wave.

The two sine waves are summed and then filtered by on-chip switched capacitor and RC low-pass filters. These guarantee all DTMF tones generated fulfil the CEPT CS203 recommendations with respect to amplitude, frequency deviation, total harmonic distortion and suppression of unwanted frequency components. A value of 00H in a frequency register stops the corresponding digital sine wave synthesizer. If both frequency registers contain 00H, the whole frequency generator is shut off, resulting in lower power consumption. A decimal value of 'x' in a frequency register yields a digital sine wave signal with frequency:

$$f = \frac{f_{xtal}}{[23(x+2)]}$$

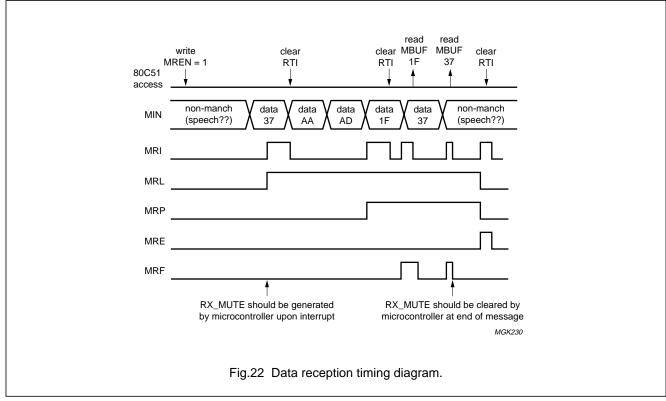

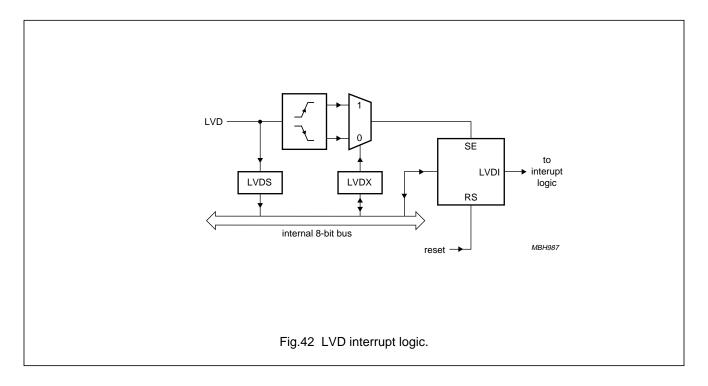

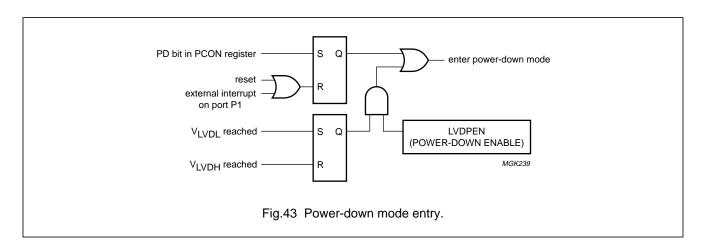

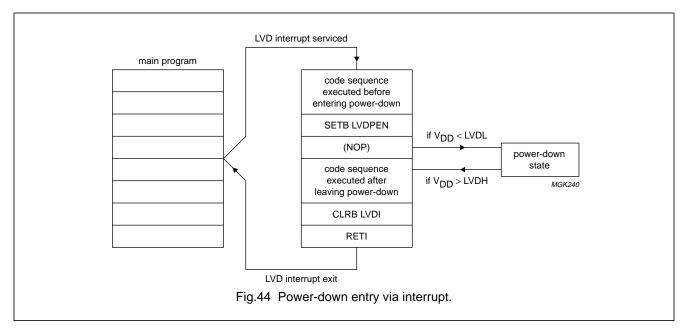

; where  $60 \le x \le 255$